大家好,我是硬件微讲堂。这是在电子星球的第10篇原创文章。

前两天,有小伙伴在群里问Buck电路的自举电容,让讲一讲。谁知道,脑门一热就答应了……既然牛皮已吹出去了,就算跪着也要写出来!如有不对或不够深入,还请包涵。

1、一道面试题

照例,先抛出来一道面试题:“Buck电路的SW引脚通常会放置一颗小电容,这颗电容有什么用?”。这个问题问得比较细,非常考验被面试者的硬件基本功。

2、似懂非懂的答案

有小伙伴可能不太清楚这颗电容的作用,回答不上来。也有小伙伴脱口而出:自举电容,用来做升压的。面试官再问的话,后面就说不出来具体逻辑。

没具体了解过,答不上来,也没啥可惜的。但是了解过一点,但又似懂非懂的这种,给出的答案只是轻轻点水或者千篇一律,那无疑是错过了一个加分项。

3、异步Buck的自举环路组成

既然是针对Buck电路讲自举电容,前面我们聊过Buck电路有异步和同步之分,想必大家对这个已经很熟悉。我们就先聊聊异步Buck的自举电容,为了更有说服力,就以TI的LMR16006为例。

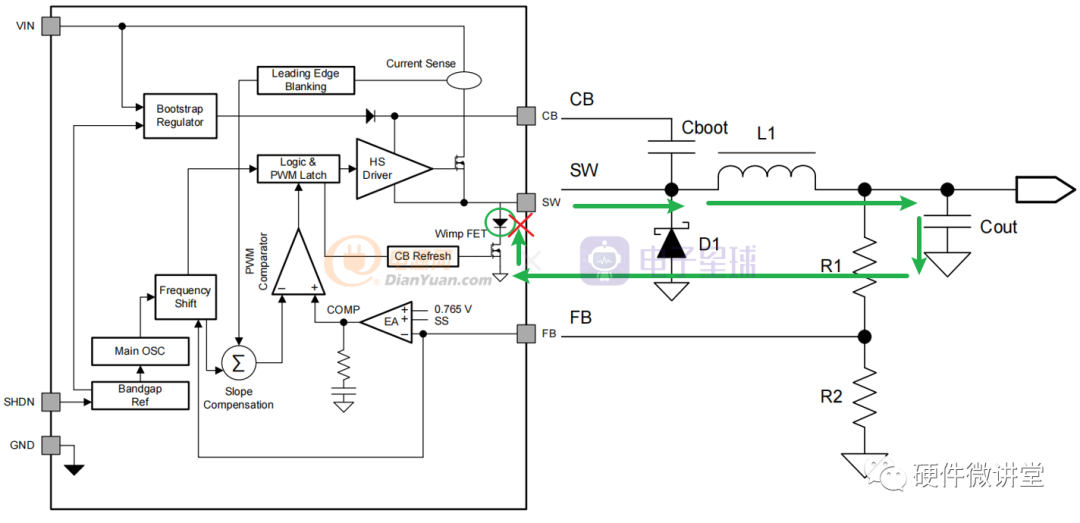

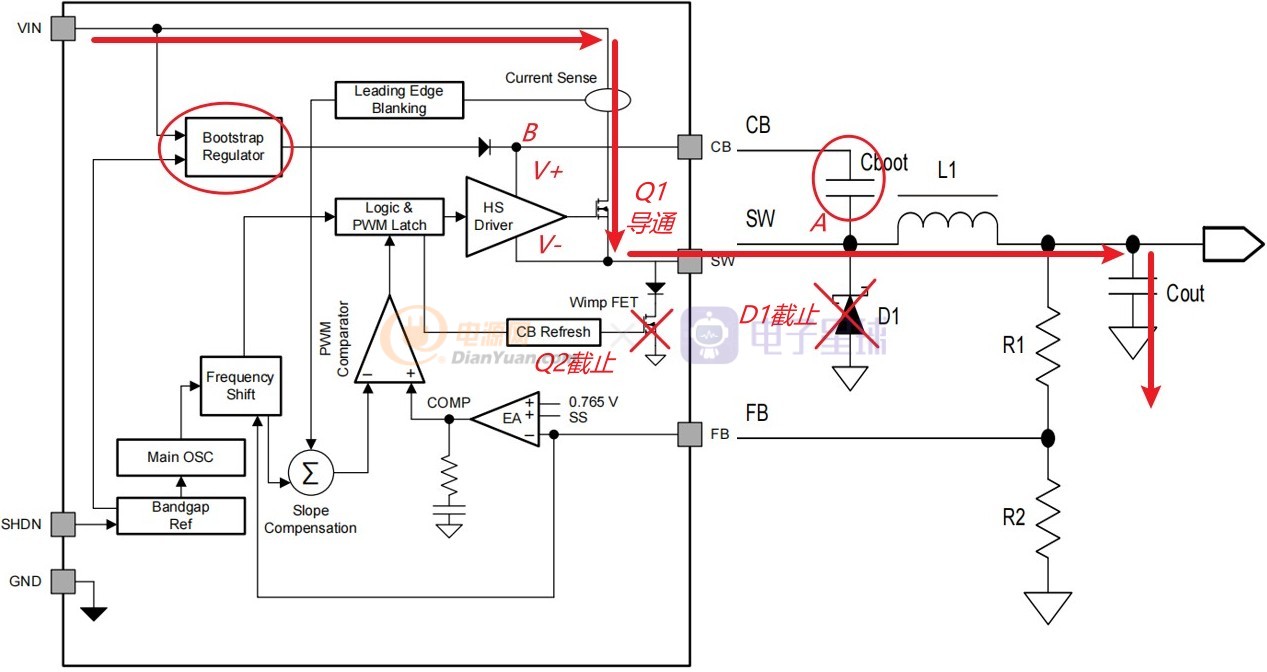

上图为芯片的典型应用拓扑,Cboot就是我们说的自举电容。为了能清楚的理解自举电容的原理,我们需要深入到Buck芯片内部,去看个究竟。

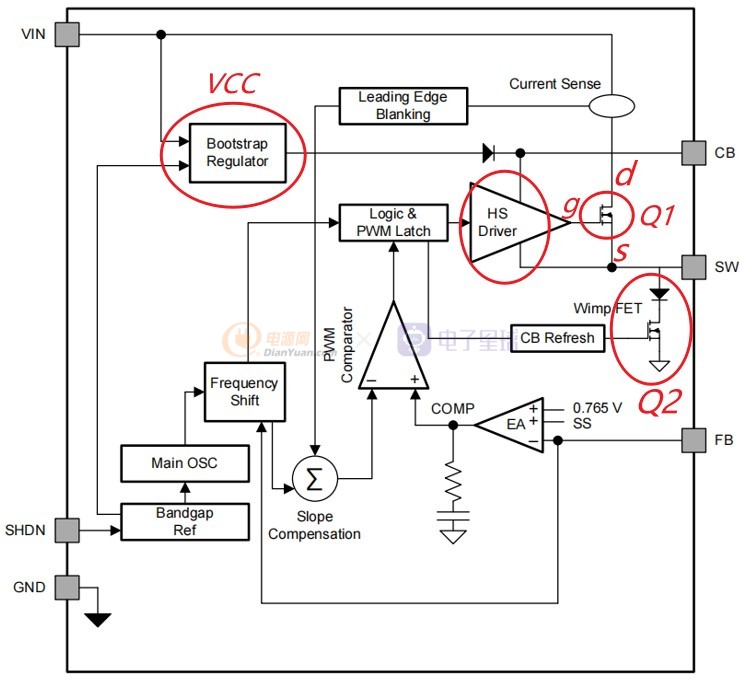

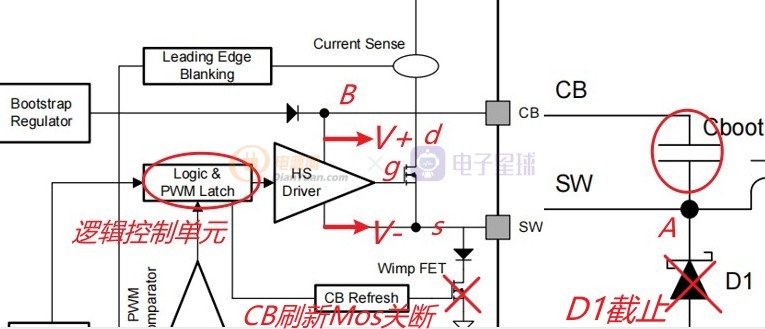

上图即为异步Buck芯片LMR16006的内部架构。今天我们主要介绍跟Cboot相关的部分,其他的不做展开。

①Q1:NMOS管,是异步Buck电路的开关管;

②HS Driver:Q1的g极驱动电路;

③Q2:NMOS管,配合CB Refresh模块,用于给Cboot电容充电提供回路;

④两个单向二极管,必要时及时截止,阻止不必要的通路;

⑤VCC:Bootstrap Regulator(自举调整器,翻译得可能不一定恰当),用于从Vin取电并给MOS管高边驱动HS Driver提供偏置电压。

LMR16006的Datasheet上并没有明确给出该Bootstrap Regulator的电压值,只是说低于3V会进入UVLO(Undervoltage lockout thresholds)状态。

4、Cboot充电回路

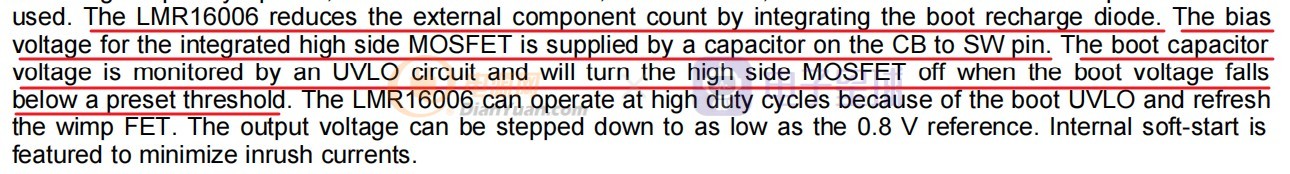

如下图所示,当高边MOS管Q1关断时,异步Buck电路的电流回路,如绿色箭头所示。这个想必大家都已经熟悉了。

在电感泄放能量的同时,Cboot也开始充电,充电的回路正如上图红色箭头所示:Vin-->VCC-->D-->Cboot-->Q2-->GND。这里我们忽略二极管D1的导通压降,就认为A点的点位约等于0电平。B点的防反二极管导通压降也忽略,那么,Cboot充电完成后的电压约等于VCC。

简单概括:电容充/电感放,各走各路!

注意:由于Q2上端有二极管的存在,不会给电感泄放提供第二个回路,所以不会影响电感的正常泄放。

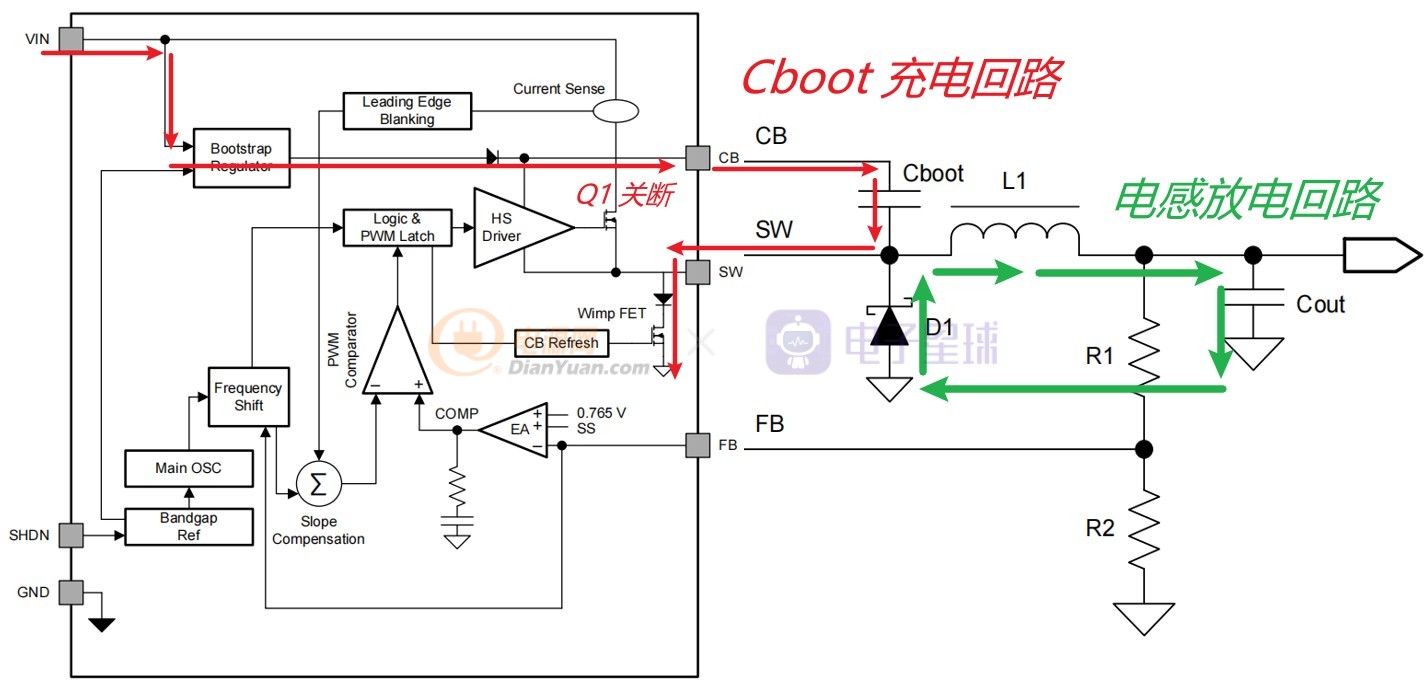

5、浮地驱动

当电感储存的能量泄放完,D1反向截止,而HS Driver要驱动高边MOS管Q1导通时,细心的你会发现:Q2的S极直接接地,G极只要输出高电平(>Vth),Mos管Q2即可导通。而Q1的S极是接在SW(即A点)上,D1已反向截止,Q2也关断,这样就没了回路,我们可以认为Q1是悬浮在半空中。只是单纯的让G极输出高电平,并不能让Q1导通。

正是由于Cboot的存在,而且并联在HS Driver电源两端,电压刚好约等于VCC。这里强调下:Cboot是并联在HS Driver的电源两端(V+/V-),并不是直接并联在MOS管的G和S两端。但HS Driver和MOS是共"参考点"(实际是V-,即A点电位)。

正是Cboot,将原本悬浮的HS Driver的两个电源端V+/V-之间建立了(电位差)联系。这个电位差刚好是VCC。

当逻辑控制单元给HS Driver输入高电平时,HS Drvier立即输出高电平(相对V-,即A点电位而言),驱动高边MOS管的G极。此时,MOS管的Vgs刚好就是Cboot两端的电压(约等于VCC),Vgs>Vth,Q1导通。

简单概括:浮地要驱动,就要加自举!

6、不突变与能持久

Q1导通后,A点电位突变为VIN,及V-电位变成VIN(远远高于VCC电压)。如果V+依旧保持VCC的电位,那Q1恐怕要被迫关闭了!正是由于Cboot的存在,Cboot电容两端电压差不能突变,B点电位变为VIN+VCC。这样对Cboot而言,电压差依然是VCC。对HS Drvier而言,以A点电位为参考,输出高电平时,Vgs依然是VCC,大于Vth,可以让Q1持续导通。

简单概况:电压不突变,导通能持久!

7、总结

聊到这里,今天想说的也差不多了,我们大概清楚了异步Buck的自举环路组成、Cboot的充电回路、浮地驱动方式以及上管持续导通的原因。

为了便于理解,概括三句话:

- 充电回路:电容充/电感放,各走各路!

- 浮地驱动:浮地要驱动,就要加自举!

- 持续导通:电压不突变,导通能持久!

以上所述,部分内容涉及个人理解,如有觉得不妥,欢迎留言讨论。

怎么样?一个简短的问题,给出的回答可浅可深,就看你对这个知识点的理解达到怎样的程度。你学废了么?

关注“硬件微讲堂”,硬件路上不慌张!