EFT标准测试的试验是脉冲施加在电源线和参考接地板之间。

对于长度大于3m的I/O电缆、信号电缆或数据电缆,通常也要使用容性耦合夹进行测试,如下图所示。

在大多数情况下,被测试的产品出现EFT问题是由滤波不充分产生的。对于适用于较低频率的滤波器,即使具有很强的滤波作用,由于其布局的问题和附近的交叉能量耦合,因此也可能在EFT产生干扰频率范围内不起作用。

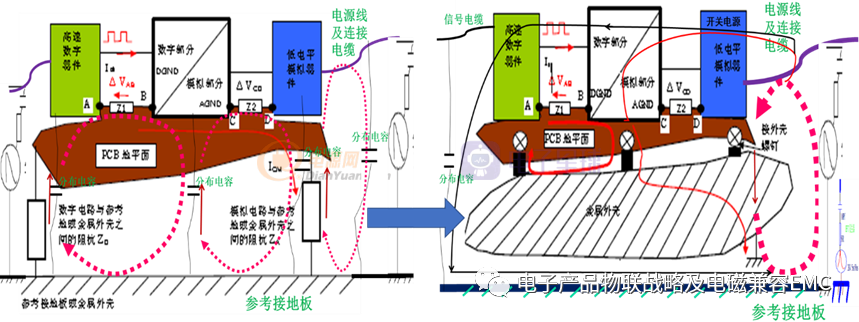

I/O线、信号线和数据线EFT测试的不合格,通常是由连接器端口缺少滤波或缺少瞬态抑制或接地设计问题而导致的;如下图所示。

(1)I/O连接器外壳和产品壳体之间的搭接阻抗不够小。

(2)电缆屏蔽层与外壳或屏蔽壳体的搭接不正确或搭接阻抗太大。

(3)电源线滤波器的滤波不充分。

(4)信号线、数据线、所有类型的输出线和所有互联电缆的滤波不充分或缺少防护设计。

(5)关键电路处射频旁路不够好,如CPU的复位线。

(6)EFT为高频现象,那么外壳不正确的屏蔽、测试线缆与其他线缆的交叉耦合噪声或各种寄生效应都可能会产生问题。

(7)由于EFT的高频特性,其电路或系统中的地走线、地回路、接地点的位置在电路板设计上就非常关键了。

典型的失效模式

(1)系统重启

(2)模拟或数字电路出现故障

(3)显示屏上出现错误的数据

(4)数据丢失

(5)数据传输停止、变慢或中断

(6)高误码率

(7)产品的状态发生改变

(8)电路受到故障

故障诊断与整改

在大多数情况下,EFT的故障诊断过程如下:

(1)通常检查电缆的屏蔽层与外壳或壳体是否搭接良好,理想情况下,它应与壳体的屏蔽层进行360度的搭接。

(2)确保所有I/O电缆连接器的外壳与EUT的壳体进行3600的搭接。这是经常出现的问题之一。

(3)电源线已进行滤波但滤波不好。或者就没有进行滤波。那么可以加装一个外置的电源线滤波器。

在理想的情况下,所有的I/O端口及直流(DC)电源或交流电源都应进行合适的滤波。对于I/O端口比如USB、以太网,通常应使用为其设计的共模扼流圈、瞬态防护装置或滤波器可以解决出现的任何问题。否则,I/O电缆或电源线电缆能将所产生的EFT电流脉冲完全地传输进电路。

如果I/O电缆、信号电缆或数据电缆存在问题,则应考虑以下措施:

(1)确保电缆屏蔽层与金属壳体进行了很好的搭接。

(2)确保连接器外壳与金属壳体进行了很好的搭接。

(3)在所有信号线或电源线与PCB的信号返回路径之间加装电容1~10nF。

(4)在所有信号线上加装共模扼流圈-为数据线所设计的。大多数质量好的以太网连接器内部都有共模扼流圈。

(5)在任何可疑的输入或输出接口上加装简单的低通RC滤波器。串联电阻为47~100Ω,输入和信号或电源返回路径之间的电容推荐值为1~10nF。

(6)如果连接器有未使用的插针,应把所有这些插针与EUT内部的壳体进行连接。浮地的插针会把辐射能量交叉耦合给其它电路,而与壳体搭接的插针能在连接器内部建立某种类型的屏蔽层。

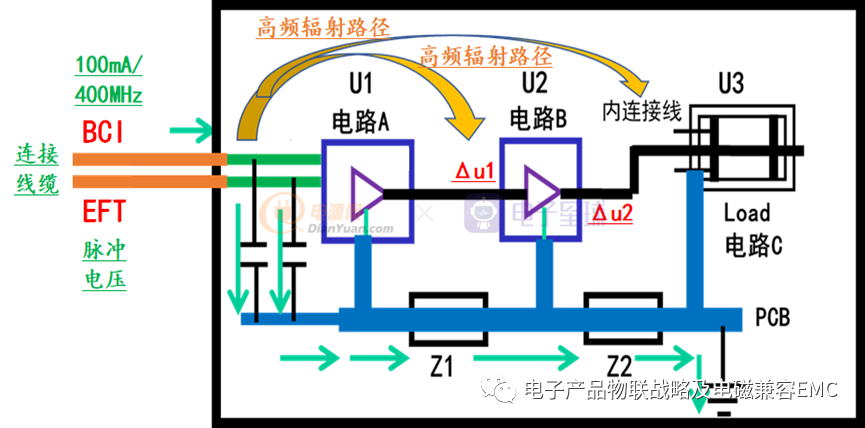

注意:当EFT干扰信号通过耦合方式到达电路板内部的时候,如下图所示:

注意:PCB的设计地走线,地回路,接地的位置 设计就是解决抗扰度EFT设计最关键的设计方法与思路。

目前行业内最典型的EMS敏感度的设计也都跟这个结构图相关联。

产品问题的发生也是跟我们产品设计可靠性相关联的。

更多的电子产品电路可靠性设计系列,会逐渐为大家解开这些设计方面的坑,让电子设计工程师少走弯路,敬请关注!