EFT标准测试的试验是脉冲施加在电源线和参考接地板之间。

对于长度大于3m的I/O电缆、信号电缆或数据电缆,通常也要使用容性耦合夹进行测试。

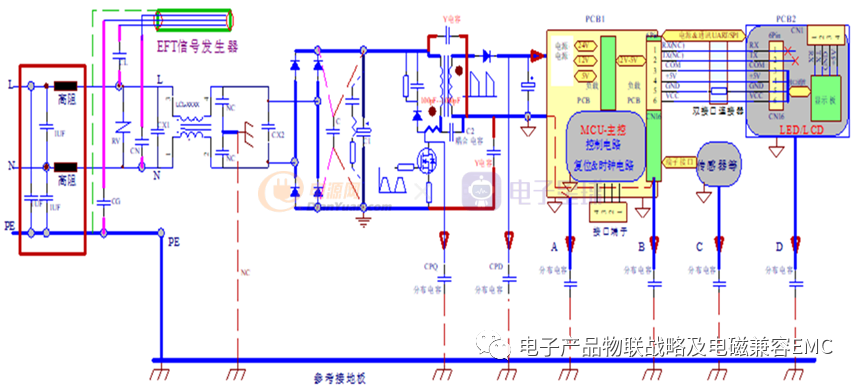

如果EFT脉冲通过电源线干扰EUT,通常在电源线的输入部分首先有开关电源部分;对于通用的应用设计可以建立等效模型-等效电路的原理架构进行电路的回流路径分析。如下图所示:

则应考虑以下的措施:

(1)尽可能在接近产品连接器的电源线上设计共模扼流圈。

(2)可以加装外置的电源线滤波器。

(3)在相线和中线之间、相线和外壳或安全地之间,以及中线和外壳或安全地之间,除了有防护器件外,还有Y电容的设计来引导共模电流的回流路径流向参考地,而不流向或减小流向后级电子电路的共模电流。

1.特殊情况及问题

对于没有金属壳体的产品或设备,EFT抗扰度的设计会比较困难。但是这种问题的设计也不是不可能的。

EFT的设计方法:阻止或转移或者两种方式都使用来处理任何的EFT电流,以避免干扰或破坏敏感电路。由于EFT在某种程度上有具有辐射效应,因此辐射敏感度中的如下一些解决方法也是适用的:

(1)最佳的方法是在所有I/O连接器上加装瞬态抑制器,它可将电流脉冲转移到PCB的信号参考平面。一定要确保PCB的信号参考平面与外壳或金属平板进行了很好的搭接。

(2)I/O线设计好共模扼流圈。如果共模扼流圈在产品里面,则需要将其放置在靠近I/O线进入设备的地方。

(3)在连接线电缆上非常靠近连接器处,加装铁氧体扼流圈,能减小一部分电流脉冲。

(4)信号线到PCB参考平面之间设计电容,或者更好的是在信号线到外壳之间设计电容,比如1nF或更小,能有助于转移EFT电流。这种电容器最好尽可能地靠近I/O连接器。一定要确保其不会滤掉这些I/O线上的有用信号或数据。

(5)对于非屏蔽的产品,通过在PCB的下面增加金属平板(或者是金属背板)对PCB周围的EFT电流进行转移。这种金属平板应与所有I/O连接器的导电后壳及外壳进行连接。通过位移电流把EFT电流转移到大地。

通过软件设计也可能使产品对EFT产生固有的抗扰度:

(1)不要使用无限的“等待”状态。

(2)在适当的情况下,使用“看门狗”程序让EUT重启。

(3)使用校验位、校验和或纠错码,以防止存储损坏数据。

(4)一定要确保所有的输入为锁存的和选通的;不能为悬空的。

2.典型的解决方法

典型的故障诊断与优化策略:

搞清楚信号回流路径 及 电流环路,很多看似诡异的现象都有迹可寻!高频特性-回流路径-噪声容限 其中回流路径进行电路等效就会有思路和方法。

(1)在可疑电缆上设计铁氧体是最快的,通常也是最先想到的方法。一定要确保这些铁氧体的位置放置尽可能地靠近产品的I/O连接器或电源连接器。

(2)对于I/O线缆、信号线或电源线需要使用低通滤波器。好的设计是在信号线上串联47Ω~100Ω的小电阻,同时在信号线与返回线或电源返回线之间使用1~10nF的电容。如果有可能,滤波器一定要使用最短的线缆。如果滤波器直接设计在PCB板上,高频时推荐使用贴装的器件。

(3)需要在敏感的内部电路上设计1~10nF的电容或RC滤波器,比如处理好任何CPU处理器的复位输入。

(4)对于以太网电缆,一定要使用具有固有共模扼流圈的连接器。

(5)对于与内部PCB相连的所有I/O线缆和电源线,最终的解决办法是设计瞬态电压抑制器或者共模扼流圈。PCB设计需要尽可能靠近在接近I/O连接器处以外壳作为基准。

(6)对于非屏蔽壳体,增加一个金属平板,所有I/O和电源连接器的外壳应与它的一面进行连接。

(7)如果问题出现在屏蔽线上,那么应确保屏蔽层在电缆两端与屏蔽壳体进行高质量的3600的低阻抗搭接。

(8)如果问题是由电路的直接交叉辐射产生的,那么应使用铝箔完全地包住整个外壳。如果这样能起作用,然后可以慢慢地剥掉铝箔直到问题再次出现。这样可以识别敏感区域的外置或外壳上产生了问题的缝隙或接合处。

(9)沿着外壳布置电缆,在输入端口附近布置的任何导线一定要使其远离这些端口。能量的交叉耦合会产生问题,把敏感电路与产生这种能量的导线隔开是一种经济的解决方法。

(10)一定要确保滤波器的安装位置靠近连接器。与其他测试一样,安装在线缆上的远端滤波器能让能量与敏感电路产生交叉耦合。

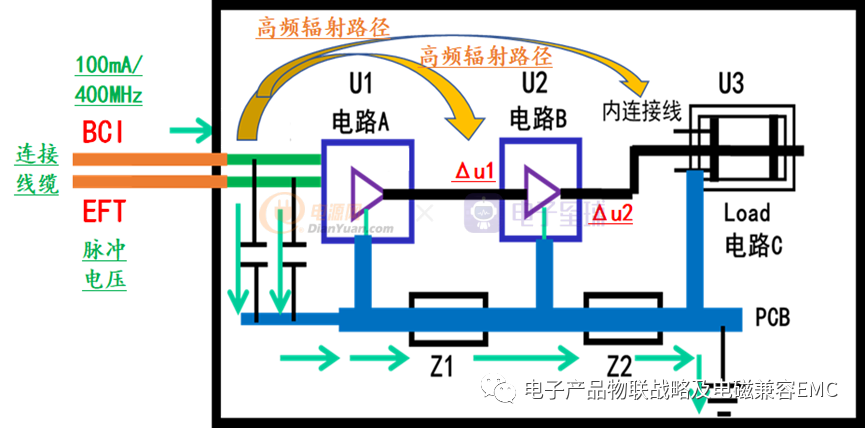

注意:当EFT干扰信号通过耦合方式到达电路板内部的时候,如下图所示:

注意:PCB的设计地走线,地回路,接地的位置设计就是解决抗扰度EFT设计最关键的设计方法与思路。

目前行业内最典型的EMS敏感度的设计也都跟这个结构图相关联。

产品问题的发生也是跟我们产品设计可靠性相关联的。

更多的电子产品电路可靠性设计系列,会逐渐为大家解开这些设计方面的坑,让电子设计工程师少走弯路,敬请关注!