滤波器系列之(二):电容

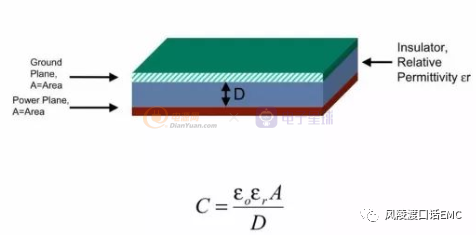

任何两个彼此绝缘又相互靠近的导体都可以构成电容器。电容是表征电容器容纳电荷本领的物理量。在两个相距很近的平行金属板中间夹上一层绝缘物质(电介质),就组成最简单的电容器,叫做平行板电容器。

图1:平行板电容与计算公式

一、电容的工作原理:

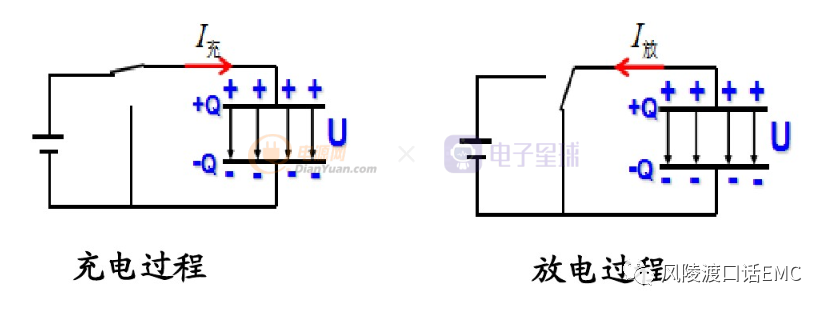

电容器是由两个电极及其间的介电材料构成,介质材料是一种电介质,当被置于两块带有等量异性电荷的平行极板间的电荷中,由于极化而在介质表面产生极化电荷,使束缚在极板上的电荷相应增加,维持极板间的电荷不变。

图2:电容充放电过程

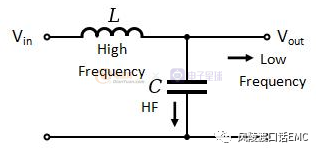

1.1、电容滤波原理

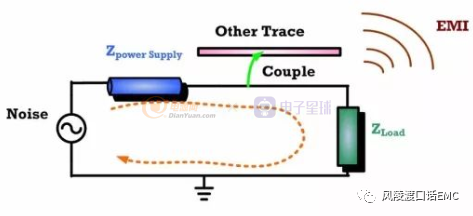

电容器具有〝通高频阻低频的特性〞,滤波是利用此特性为干扰频点提供〝低阻抗路径〞。由于电容本身不具有消耗能量的特性,干扰频点只是通过电容改变了传播路径而已,故电容元件又称反射式滤波元件。

图3:电容滤波原理

任何信号只有构成回路才能产生电流,回路面积越小产生的EMI干扰就越小,而回流面积取决于信号路径长度,以及回流路径长度,信号布线长度与回流路径长度构成的回路面积越小越好,通过增加高频电容来缩短信号回流面积是解决EMC问题的杀手锏之一。

干扰实质上并没有穿过电容到地消耗掉,而是类似电池充电,干扰被吸收到电容两端,电容容值大小改变的是电荷移动的速度,也就是充放电的速度;简单理解电容旁路的原理就是干扰在很小的路径范围内重复移动轨迹。

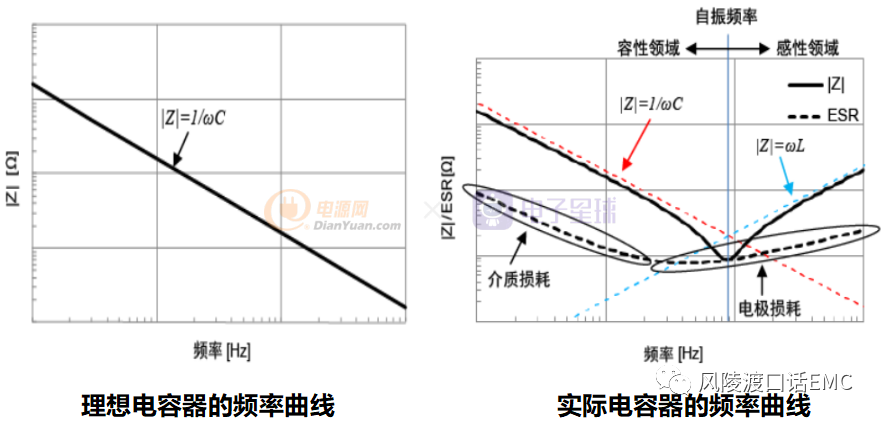

1.2、电容的频率特性

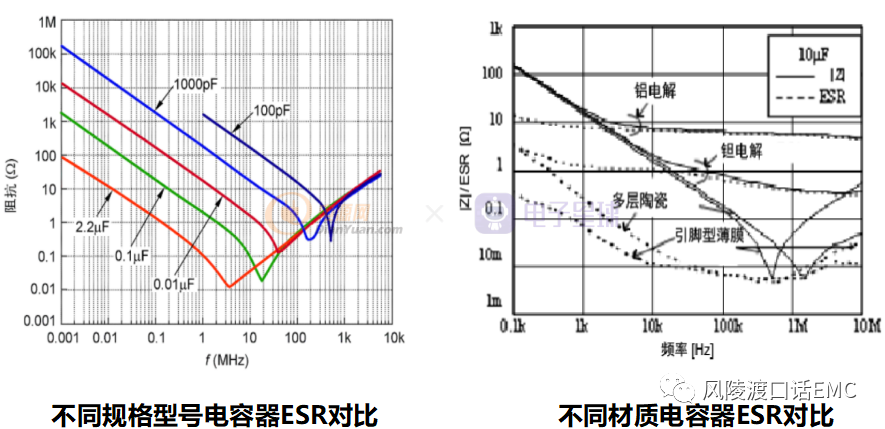

图4:电容的频率特性对比

1.2.1、电容容性区域&感性区域:

低频范围内非常接近理想电容器,阻抗与频率成反比,此区域称为容性区域。随着频率的改变,阻抗却成升高趋势,电容的寄生电感影响非常明显,此区域称为感性区域。

电容的ESR与ESL:

图5:电容的电路等效模型

ESR是Equivalent Series Resistance的缩写,翻译过来就是等效串联电阻,电容的ESR就是电容串联等效电阻。

ESL是Equivalent Series Inductance的缩写,翻译过来就是等效串联电感,电容的ESL就是电容串联等效电感。

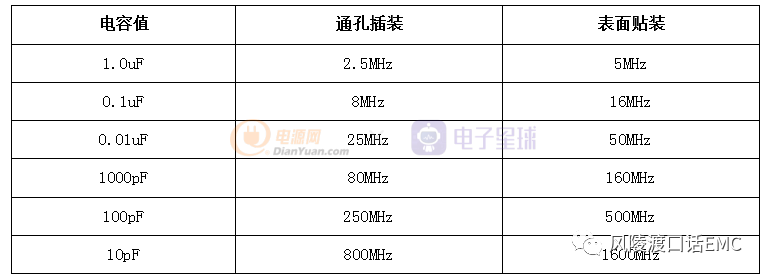

图6:电容的ESR曲线对比

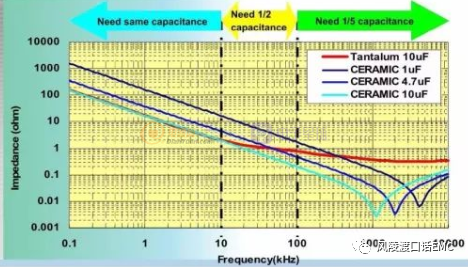

要得到更好的EMC滤波特性,电容具有低ESR是很重要的;由于电容自身的谐振点,所以电容并联使用时,拓宽通频带的同时,也产生新的反谐振点;为减少反谐振点的个数,选择滤除不同频段的电容时,相邻容值最好相差100倍的量级。

1.2.2、自谐振频率(Self Resonant Frequency):

阻抗最小值时的频率称为自谐振频率,此时Z=ESR,电容的自谐振点也是阻抗最低点。

1.2.3、电容ESR/ESL的影响因素

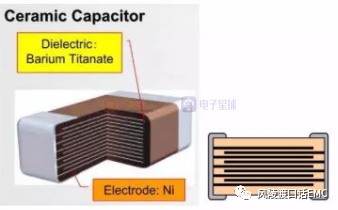

贴片电容的叠层结构

图7:贴片叠层结构对ESR的影响

内部电极层数越多,意味着层间电阻并联越多,即阻抗越小,同样道理ESR就越小。

材质的电阻率

ESR与材质的电阻率相关,不同材质ESR不同,ESR越小,便能使噪声被旁路的越多,即插入损耗越大,噪声抑制能力就越好。

图8:材料的电阻率对ESR的影响

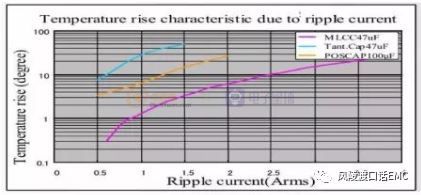

ESR会将纹波电压,转换为热能,若ESR越高,则转换的热能就越多;随着纹波电压的增大,电容温度上升,ESR越大温度上升就越多。温度上升,电容值也会有所下降,不同材质的电容,随温度升高时电容值的稳定性不同。

图9:ESR对纹波电流的影响

二、电容应用要点说明

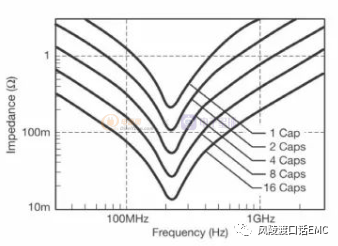

2.1、多颗同规格电容并联使用

如果单颗电容的纹波电压耐受度不够,则可以选择多颗电容并联使用,并联电容数量依据纹波电压需要;多颗同规格电容并联使用,除了可以降低纹波电压,也可以降低ESR,增大插入损耗。

图10:不同数量同规格电容并联使用阻抗曲线

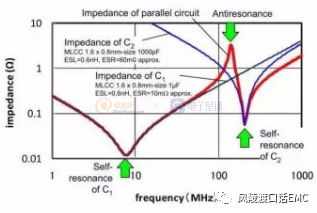

2.2、多颗不同规格电容并联使用

当噪声的频率范围很宽时,单个电容的滤波频带无法满足滤波要求,则需要使用不同规格的电容拓宽通频带。多颗不同规格电容使用时,不同电容的感性区域与容性区域又会产生交叉点,该交叉点正好会产生并联谐振,使滤波阻抗变大降低了滤波效果,该交叉点称为反谐振。

图11:不同规格电容并联使用阻抗曲线(存在反谐振点)

因此,并联不同容值的电容时,其电容值差距应充分考量,建议电容容值差是100倍量级,最小差不允许小于10倍量级,以降低反谐振点滤波阻抗。

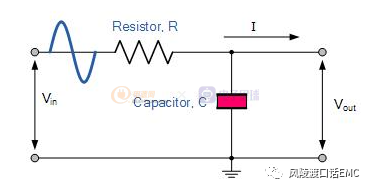

2.3、使用电容组成低通滤波器

电容通常与电感、磁珠、电阻元件组成低通滤波器,滤除信号线、电源线上高频噪声,低通滤波器参数设计时应结合信号工作频率、高频噪声频率选择合适的电路结构。

图12:RC低通滤波电路

图13:LC低通滤波电路

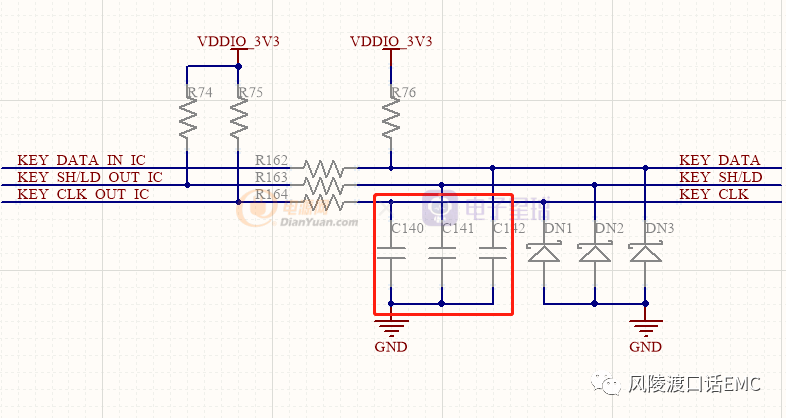

2.4、端口信号旁路电容

为防止PCB内部干扰噪声沿着连接线缆耦合,形成天线向外辐射干扰,通常会在PCB接口电路增加高频旁路电容,将板内干扰通过电容旁路回到源端,同时也防止外部的干扰噪声进入板内,耦合干扰到板内敏感信号。

图14:电容应用于端口信号高频旁路

2.5、芯片供电电源退耦与高频旁路

芯片供电电源退耦:

半导体制造工艺的持续提升,芯片工作频率持续提高,芯片处理数据时的快速切换,电流突变会引起供电电压下降,相当于纹波电压。在芯片供电电源引脚上增加退耦电容,快速补偿芯片供电电源引脚因高频开关引起的电压跌落,通常使用的电容相对较大。

图15:电容应用于芯片供电电源退耦

芯片高频噪声旁路:

半导体制造工艺的持续提升,芯片工作频率持续提高,芯片处理数据时的快速切换,在芯片供电电源线上产生高频噪声干扰,高频噪声进入芯片内部不同模块电路时,会引起模块电路间的相互干扰。

高频噪声形成的高频电流环路,不加以控制则会引起EMI问题,为切断高频噪声耦合路径,需要在芯片供电电源引脚上增加高频旁路电容,使高频噪声以最小环路面积回流到源端,改善EMI问题和芯片模块间串扰问题。

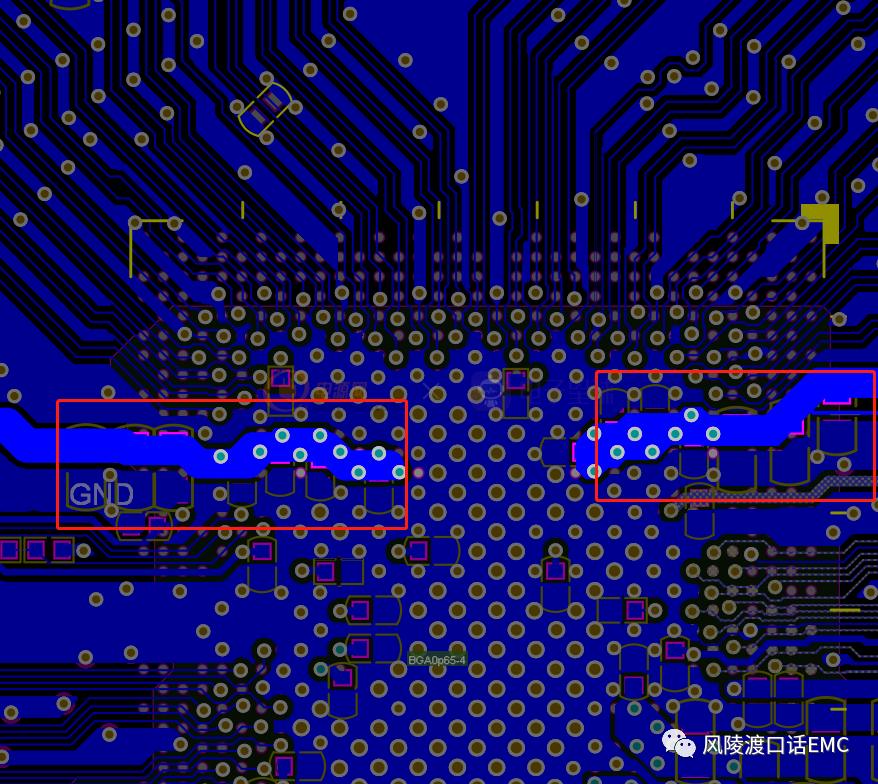

2.6、芯片退耦或旁路电容的PCB设计要点:

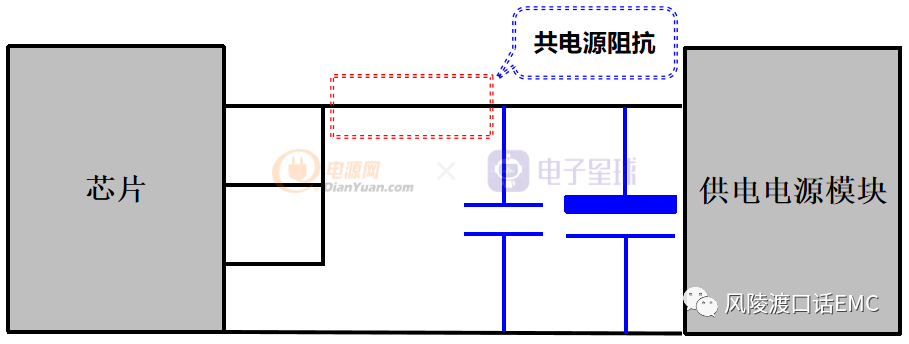

图16:退耦电容或者旁路电容引起共阻抗耦合

供电电源引脚通常在原理图设计阶段会放置两颗电容,甚至更多。PCB Layout设计时应将高频电容靠近芯片引脚放置,大容量电容或者电解电容则可以距离芯片供电电源引脚稍远,主要是高频布线寄生电感的影响。当多个电源引脚远离滤波电容较远时,不同引脚会因为共用一段PCB布线而形成共阻抗耦合,如上图所示。

2.6.1、单点汇流解决共阻抗耦合:

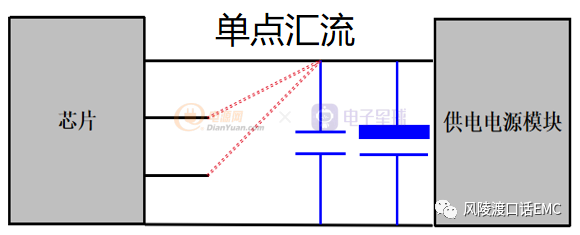

图17:不同电源引脚共用滤波电容时单点汇流解决共阻抗耦合

低成本设计时,芯片相同电压的供电电源引脚共用滤波电容时,每个电源应单点布线在滤波电容处回合,避免共阻抗耦合,如上图所示。

2.6.2、不同供电电源引脚单独退耦解决共阻抗耦合:

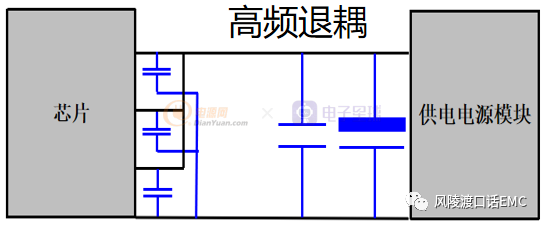

图18:不同电源引脚单独退耦解决共阻抗耦合

芯片不同供电电源引脚使用单独的高频电容进行高频退耦,而低频退耦或者滤波则可以共用滤波电容,这是因为低频寄生电感的影响可以忽略不计。

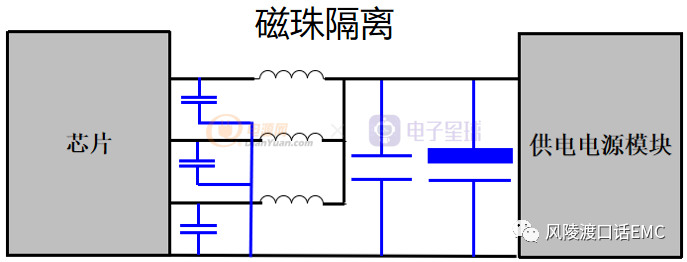

2.6.3、不同供电电源引脚单独退耦+磁珠隔离解决共阻抗耦合:

受限于芯片内部供电电源引脚内阻的影响,有时候高频的退耦和旁路效果不理想时,则可以采用不同电源引脚单独退耦并增加磁珠进行高频衰减隔离的对策来解决共阻抗耦合的问题。