1.DDR

DDR是Double Data Rate的缩写,即“双比特翻转”。DDR是一种技术,中国大陆工程师习惯用DDR称呼用了DDR技术的SDRAM,而在中国台湾以及欧美,工程师习惯用DRAM来称呼。DDR的核心要义是在一个时钟周期内,上升沿和下降沿都做一次数据采样,这样400MHz的主频可以实现800Mbps的数据传输速率。我们看下各个版本的速度对比

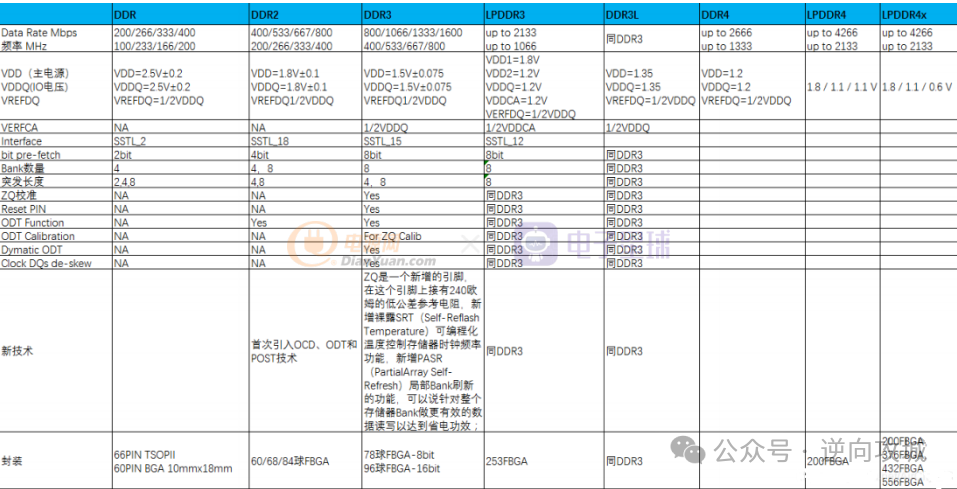

从上可以得知,每个版本对应的工作频率有多种,当然硬件跟软件不一样不必知道这么清楚,只需要知道几个常规频率就好。

很多知识点的梳理,大家网上能找到大篇幅的参考,本文就说几个常用的和面试中面试官最喜欢问的几个点来讲。

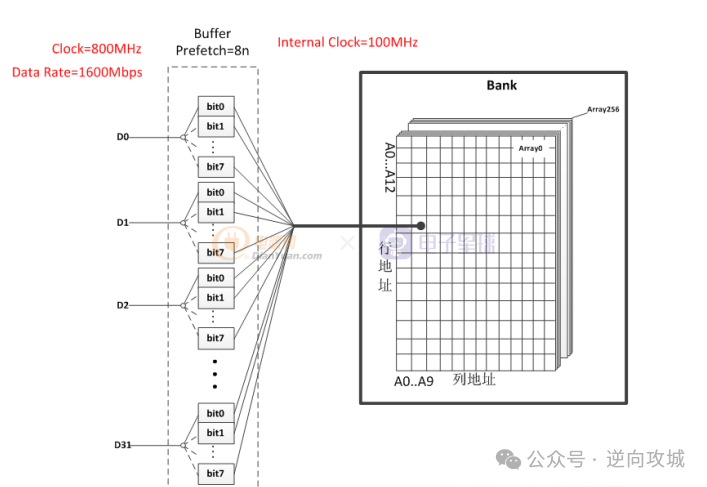

VTT为DDR的地址线,控制线等信号提供上拉电源,上拉电阻是50Ω左右。VTT=1/2VDDQ,并且VTT要跟随VDDQ,因此需要专用的电源同时提供VDDQ和VTT,在Fly-by的拓扑中,VTT提供电流,增强DDR信号线的驱动能力。 DDR3的时钟是800MHz,Data Rate是1600Mbps,由于这个Buffer的存在,DDR内部的时钟只需要200MHz就可以了(注意DDR内部不是双比特翻转采样)。

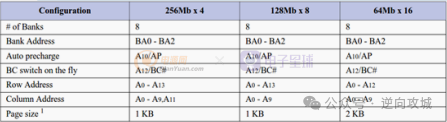

DDR内部的最小存储单元(1bit)是一个晶体管+一个电容,电容会放电,需要不断的“刷新”(充电)才能保持正常的工作状态,由于电容充放电需要时间,DDR内部的频率受限于此,目前技术一般在100~200MHz。因此需要用Prefetch技术来提内部数据高吞吐率(其实就是串并转换原理)。Prefetch位宽的提高,是DDR2,3,4非常显著的变化。1.DDR的容量计算:DDR3 1Gb的寻址配置,以其中128Mbx8为例说明,其中x8表示IO数据(DQ)位宽度。

2.ODT

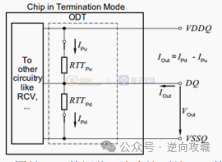

是内建核心的终结电阻,它的功能是让一些信号在终结电阻处消耗完,防止这些信号在电路上形成反射。换句话说就是在片内设置合适的上下拉电阻,以获得更好的信号完整性。被ODT校准的信号包括:DQ, DQS, DQS# and DMfor x4 configurationDQ, DQS, DQS#, DM, TDQS and TDQS# for X8 configurationDQU, DQL, DQSU, DQSU#, DQSL, DQSL#, DMUand DML for X16 当一个CPU挂了很多个DDR芯片的时候,他们是共用控制线,地址线的,走线肯定要分叉,如果没有中端匹配电阻,肯定会产生信号完整性问题。那么如果只有一个DDR芯片的时候,需不需要呢?正常情况下,走线很短,有符合规则,是不需要的。下图是DDR中的IO上下拉电阻,RON是DDR的输出结构的上下拉电阻,RTT是DDR输入结构的上下拉电阻。这两个电阻的阻值都是可调的

DDR3的PIN定义上有一个引脚是ODT,如果ODT=0,DRAMTermination State功能关闭;ODT=1,DRAMTermination State的功能参考寄存器设置。因为DRAM Termination State非常耗电,所以不用的时候最好不要打开

3.ZQ信号

在DDR3时代开始引入,要求在ZQ引脚放置一个240Ω±1%的高精度电阻到地,注意必须是高精度。而且这个电阻是必须的,不能省略的。进行ODT时,是以这个引脚上的阻值为参考来进行校准的。校准需要调整内部电阻,以获得更好的信号完整性,但是内部电阻随着温度会有些细微的变化,为了将这个变化纠正回来,就需要一个外部的精确电阻作为参考。

4.OCD

是在 DDR-II 开始加入的新功能,而且这个功能是可选的,有的资料上面又叫离线驱动调整。OCD的主要作用在于调整 I/O 接口端的电压,来补偿上拉与下拉电阻值, 从而调整DQS 与DQ 之间的同步确保信号的完整与可靠性。 调校期间,分别测试 DQS 高电平和 DQ高电平,以及 DQS 低电平和 DQ 高电平的同步情况。

如果不满足要求,则通过设定突发长度的地址线来传送上拉 / 下拉电阻等级(加一档或减一档),直到测试合格才退出 OCD 操作,通过 OCD 操作来减少 DQ 、 DQS的倾斜从而提高信号的完整性及控制电压来提高信号品质。由于在一般情况下对应用环境稳定程度要求并不太高,只要存在差分 DQS时就基本可以保证同步的准确性, 而且 OCD 的调整对其他操作也有一定影响, 因此 OCD 功能在普通台式机上并没有什么作用,其优点主要体现在对数据完整性非常敏感的服务器等高端产品领域。

5.DDR走线

DDR的信号线需要分组:-数据线一组(DQ,DQS,DQM),误差控制在20mil以内;-控制线一组(Address,控制线,时钟),以时钟为中心,误差控制在100mil以内。

小结:

1.DDR本人目前使用得中觉得三星得确实稳定好用,其他基本都是东芝,海力士等等老外得品牌,国产用的相对较少。

2.DDR还有一个致命问题,每一批做出来的板子需要重新适配DDR,否则容易工作不稳定,这也是多数人遇到的问题,目前来说没啥解决的好方案,面试的老司机套方案也是套不出来的,这跟PCB的制程,制造工艺有关,暂无好的解决办法,欢迎大家留言说说有啥办法解决每一批板子的差异。

3.DDR走线目前常规的两种是T型或者菊花链的拓步走线方式,这里还是奉劝大家,严格按照厂家推荐走线拓扑,最好能直接对抄,这一块问题比较多,走线麻烦复杂,重新打板周期也长,成本也不小,不要轻易尝试,除非你想多麻烦一下软件兄弟,调半天都不稳定。