一、PCB布局要点:

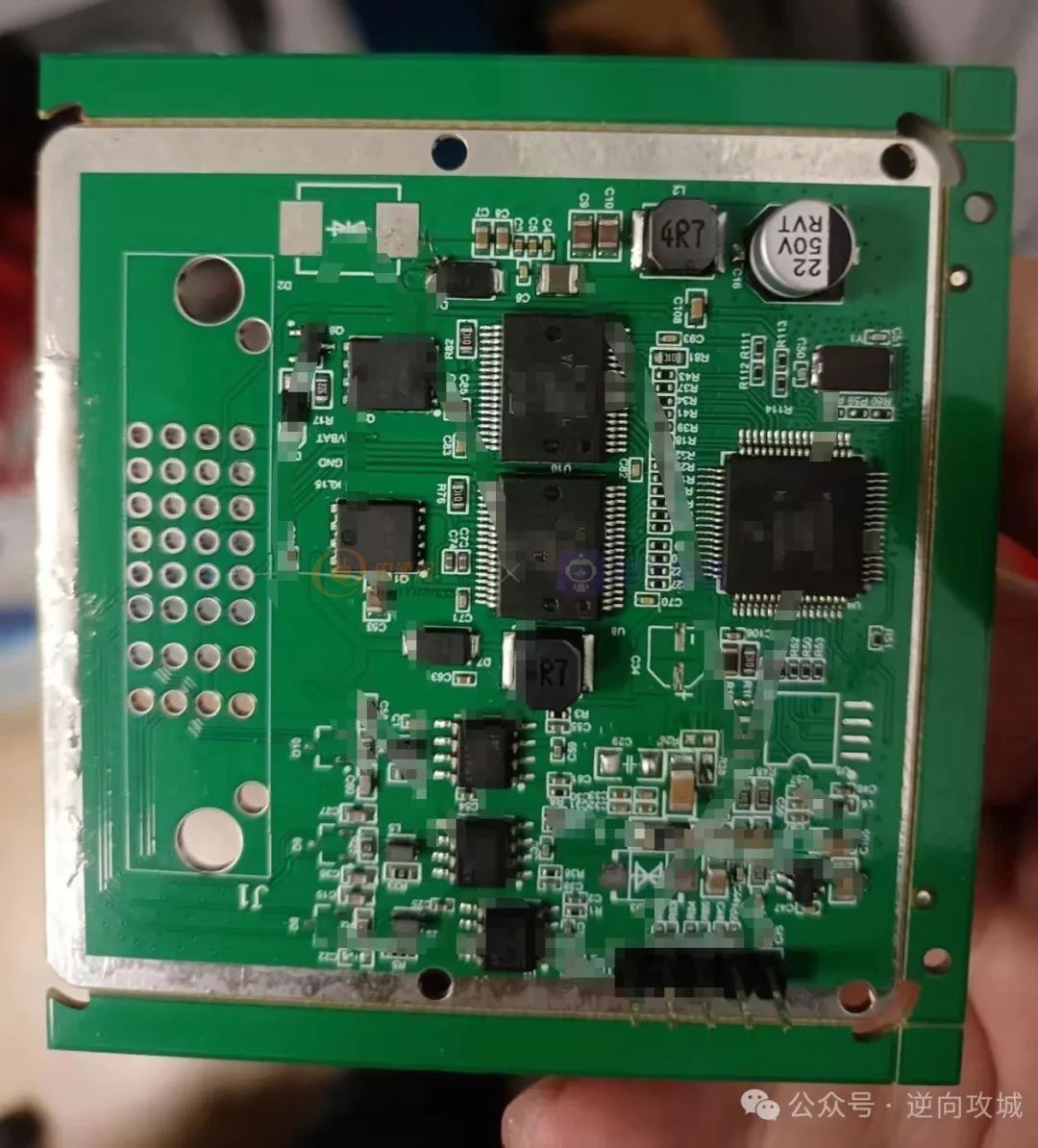

在 PCB 布局时要结合机械结构尺寸约束,认真考虑各个功能模块电路和具体器件的摆放。微弱信号模拟电路、高速数字电路和大噪声电路必须分开,以减少电子电路间的耦合干扰。放置器件时要综合考虑不同模块电路信号走线是否会存在交叉混合的情况。

1.电压调节器和电源放在接近电源输入口,不要将电源信号与高噪声信号并行走线。

2.敏感器件,如微控制器芯片、晶振不要放在 PCB 边沿;将连接接口放在 PCB 边沿。

3.进行布局时,尽可能缩短功能组件中各个器件的物理距离。

4.易受干扰的元器件相互间不能太近,输入输出元件要远离。

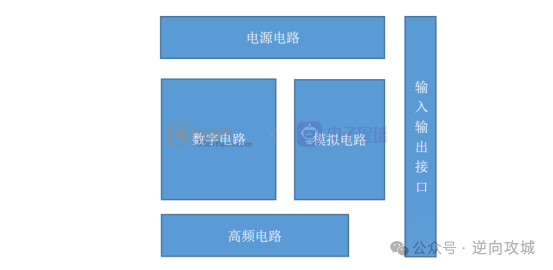

电路功能模块布局

一般会这样布局,然后在板端边沿留出覆裸铜边沿

二、电源和地

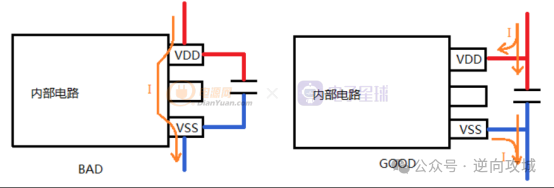

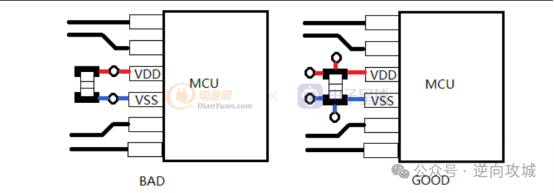

通常微控制器芯片的 VDD/VSS 引脚应以星形的方式进行布线,不要以链的方式连接。如果是多层板,VDD 和 VSS 应该通过内层电源和地平面进行连接。推荐在芯片正下铺设数字地平面。

避免走直角,后面会单独做一期仿真来看信号质量

三、去耦电容的处理去耦电容尽可能的靠近 VDD 引脚,如果摆放的太远就失去了去耦的功能。从 PCB 板上供电 LDO 出 来到微控制器芯片电源入口处添加 μF 级的旁路电容(一般频率在10M以下),以缓冲公共电源线路中的电压波动和旁路电源噪声。当使用小的陶瓷电容和大的电解电容并联去耦时,将陶瓷电容更靠近芯片 VDD 引脚以最小化环路面积。如果可能,将所有的去耦电容放在和微控制器芯片同一层(具体问题具体分析,有时候还得分层摆放),或者放在成对电源引脚(VDD/VSS)下面的底层。电源走线要先经过去耦电容焊盘再到 VDD引脚,这样噪声电流就会被过滤掉。

请勿将电源过孔放置在去耦电容和 VDD 引脚之间,这样会使去耦电容效果打折,这是很多新手和老手容易犯的错误。

四、信号线

在布置完电源和地的走线后,优先布局晶振的走线。当电路中有数字模拟混合信号时,走线不要混合交叉。优先处理敏感信号的布线,并且要对敏感信号进行保护以避免干扰。在微控制器芯片外围电路中敏感的信号包括:时钟、复位和中断信号线。

1.尽可能缩短并行走线的长度。

2.如果各信号需要交叉走线,请确保它们垂直交叉,从而最小化各信号间的耦合电容(大家应该知道为什么要垂直)。

3.保证各个信号线间的距离符合“3W”原则,以得到最小耦合电感。

五、晶振

晶体振荡器在启动时对干扰特别敏感,强烈建议晶振信号线不要与大电流开关线路并行走线。一般准则如下:

1.负载电容尽量靠近 HEXT_IN/HEXT_OUT 引脚,并用地环保护,包地打孔。

2.不要在晶振电路附近或横跨电路底层走任何信号线(地线除外)。

3.选择满足系统要求的最小频率晶振。

4.使用合适的负载电容。

5.将晶振外壳接地。

六、模拟信号

低电平的模拟信号很容易被数字信号干扰。如果模拟和数字信号必须混合,请确保线路正交走线,以减少耦合效应。如果微控制器芯片的 VDDA/VSSA和 VREF+/VREF-没有和数字电源、数字地进行隔离或者没有进行滤波处理会严重影响 ADC 的性能。

七、输入输出端口

相比输出端口,配置为输入功能的 GPIO 对噪声更加敏感。建议输入功能 GPIO 上添加 RC 滤波器,用于衰减外部噪声,滤波器的位置要靠近引脚。RC 的取值 取决于输入信号的特征,串联电阻值一般在 100 Ω ~ 1 kΩ,滤波电容一般 1 nF ~ 0.1 μF。NRST 引脚外接退耦电容和上拉电阻的布局都应被当做电源引脚滤波,应最小化电容的接地环路和上 拉电阻的 VDD 环路。

未使用的 GPIO 引脚处理:

1.如果保持悬空,请在软件中设置为输出模式并输出低电平。

2.如果不悬空,请将未使用的引脚接一个 10 kΩ 下拉电阻。

3.不建议将未使用的 GPIO 引脚直接连接到电源或者地。

八、EMC设计注意事项

1.用多层板;

2.在每个对应的电源引脚附件放置一个或者两个去耦电容,以减少可能的干扰;

3.用电容器组匹配电源去耦的频率特性;

4.确保只有一个星形接点将模拟地和数字地进行连接,该星形接点尽可能远离微控制器芯片;

5.尽可能靠近线性电源调节器的旁路电容;

6.将模拟输入信号用模拟地进行隔离处理;

7.避免大面积地环路;

8.确保换层的电源走线至少有两个过孔进行连接;

9.在对应的引脚或接口线上采用保护器件;

九、差分布线

1、当保留了铜皮,并且铜皮没有连接到GND上时,串扰是最大的。

2、当保留了铜皮,并且连接到GND,即保留了“保护地”,但是如果没有按照十分之一波长加地孔,多家地孔,否则串扰也会比较大

3、保留铜皮,并且连接到GND,,即保留了“保护地”,并且按照十分之一波长加地孔,则串扰会更小,效果最好。

4、如果有足够的空间,删除铜皮,即:不加保护地,其结果也相对比较好,但是会比按十分之一波长加地孔大一些。

小结:

1.强电和弱电一定要隔离,留有充足的爬电空间或者直接打通孔隔开,一般是2mm(220V),按照电压高低可以继续扩大,一般高压小电流或者高功率产生的电弧距离较远,这个时候要做灭弧电路;

2.模拟和数字不一定要把GND隔离开,看具体需求,一般的MCU就别瞎整,听各种老司机的经验就是作死,数字和模拟地就搞在一起,不要隔离,增大地平面,切莫一开始就搞多个地,信号乱七八糟的,没有根据的口口相传,这也是多个公司和老司机做事风格的弊端,没说不好,就是容易误导人。(具体什么情况要隔离开,一起分享交流)

3.发现问题从理论分析所有可能性,按照排除法,切莫用实验次数打败理论支撑,找找身边老司机,这个时候老司机的重要性就出来了,老司机只能参考,常说的stay foolish, stay hungry!!!