最近使用ADI公司的LT1683设计一个开关电源。出现较大问题,特来请教各位大神。输入24V,输出±7V,其中+7V电流为5A,-7电流较小,和忽略。磁芯EFD25,材料PC40。推挽变压器,主副比为14:5,感值460:45uh,开关频率99K左右,原理图如图7,抱歉有点模糊,但还能看清。![]()

变压器绕线采用0.32漆包线,输入两根并,输出三根并,所以主边四根并绕,两侧三毫米格条。次变6根并绕。(主副边都超过1层,但第二层线很少,不确定是否有问题,或者怎么改善)

第一次设计,所以欠考虑,CS脚处理不太好,现在打算改版,但是问题没有全找到,所以有些疑惑,为改版提供依据。

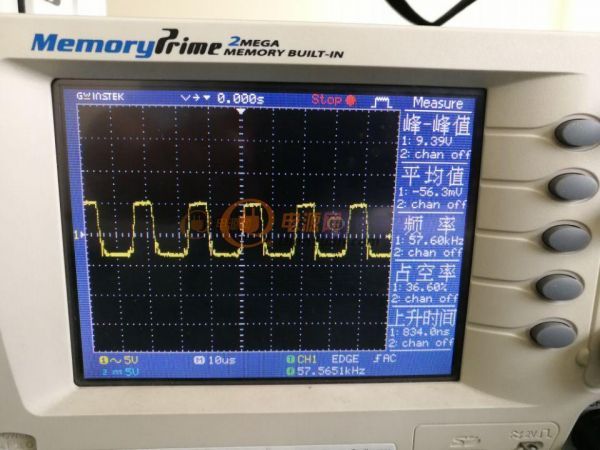

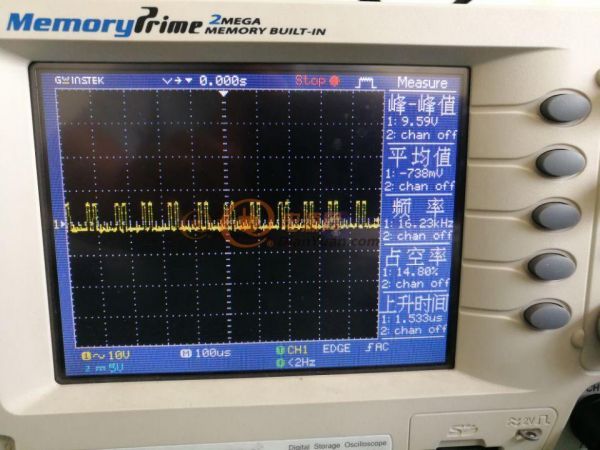

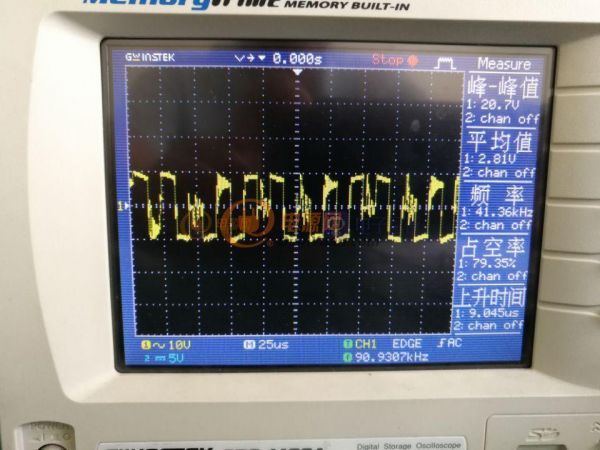

问题描述如下:我做了测试,分别拍了3组图片,所有波形均是对地测试(数字地模拟地通过0欧电阻连接)。测试条件,cs电阻0.04欧(估算完全够用),rt=16.9k,ct=1.3n,计算得开关频率为99.2K,所以mos管栅极频率为49.6k。输入电压24v,输出7v。图一为负载20.6欧时mos管的栅极波形,图二为对应的整流管输入端波形。频率是正常的,随着负载加重,从某一刻开始,频率开始改变,先跳变到78k,随着负载继续增大,频率开始降低。当再次降到49k时(此时负载为5.7欧),输出电压开始下降(从7v开始逐渐降低),波形开始混乱。如图5图6所示。图三和图四为开关频率改变阶段的一个示例。图三为负载6.8欧时mos管栅极波形,图四为对应的整流管输入端波形。

疑惑:1)明明是脉宽调制器件,为啥频率会改变

2) 图2的波形咋会事,是否正常。

3) 加载太重后,竟然降电压,波形混乱,疑似自激。可能是哪些导致的问题。

4) 变压器是否有致命缺陷?

5) CS脚是否有设计缺陷。

图1

图2

图3

图4

图5

图6

图 7