最近参加一个职业考试,有这样一套题------什么是同步电路和异步电路?你会的整流和升压方式有哪些?什么是同步整流和同步升压?为什么同步整流或者同步升压的效率会更高?

同步电路和异步电路的区别

一、原理不同

同步电路利用时钟脉冲使其子系统同步运作,而zhi异步电路不使用时钟脉冲做同步,其子系统是使用特殊的“开始”和“完成”信号使之同步。

二、优点不同

由于异步电路具有下列优点--无时钟歪斜问题、低电源消耗、平均效能而非最差效能、模块性、可组合和可复用性--因此近年来对异步电路研究增加快速,论文发表数以倍增,而Intel Pentium 4处理器设计,也开始采用异步电路设计。v异步电路主要是组合逻辑电路,用于产生地址译码器、FIFO或RAM的读写控制信号脉冲,其逻辑输出与任何时钟信号都没有关系,译码输出产生的毛刺通常是可以监控的。同步电路是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有操作都是在严格的时钟控制下完成的。这些时序电路共享同一个时钟CLK,而所有的状态变化都是在时钟的上升沿(或下降沿)完成的。

三、分析不同

异步时序逻辑电路分析时,还需考略各触发器的时钟信号,当某触发器时钟有效信号到来时,该触发器状态按状态方程进行改变,而无时钟有效信号到来时,该触发器状态将保持原有的状态不变。同步逻辑有两个主要的缺点:1、时钟信号必须要分布到电路上的每一个触发器。而时钟通常都是高频率的信号,这会导致功率的消耗,也就是产生热量。即使每个触发器没有做任何的事情,也会消耗少量的能量,因此会导致废热产生。2、最大的可能时钟频率是由电路中最慢的逻辑路径决定,也就是关键路径。意思就是说每个逻辑的运算,从最简单的到最复杂的,都要在每一个时脉的周期中完成。一种用来消除这种限制的方法,是将复杂的运算分开成为数个简单的运算,这种技术称为“流水线”。这种技术在微处理器中非常的显著,用来帮处提升现今处理器的时钟频率。

emmmmmm

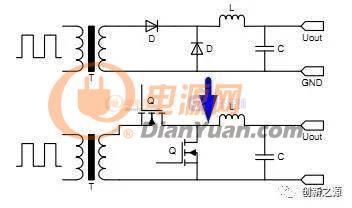

我先以我比较熟悉的反激为例说吧,目前自己用的比较多的有两种:

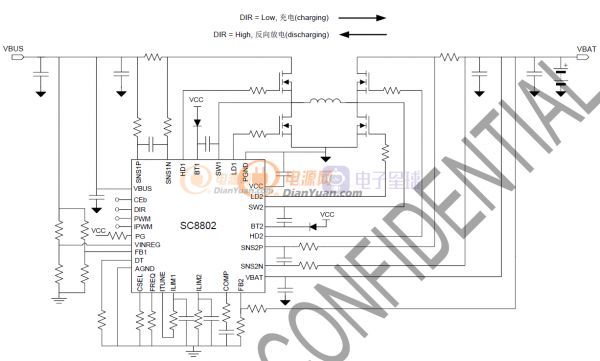

1、同步整流芯片绕组斜率检测,原边MOS管关断瞬间绕组电压反向(产生较大的dv/dt),芯片检测此信号打开脉冲给到输出整流MOS管(MOS管电流方向要S-D,在同步整流不打开情况下走体二极管),当电流下降到0时,产生谐振,检测绕组电压降低,脉冲关断防止倒灌。

2、自驱同步整流:也是利用开关瞬间的绕组大的dv/dt,不过此绕组后接微分电路,在产生瞬间给到MOS管驱动Qg供电,当进入DCM因为谐振,也会抽取Qg使其关断。

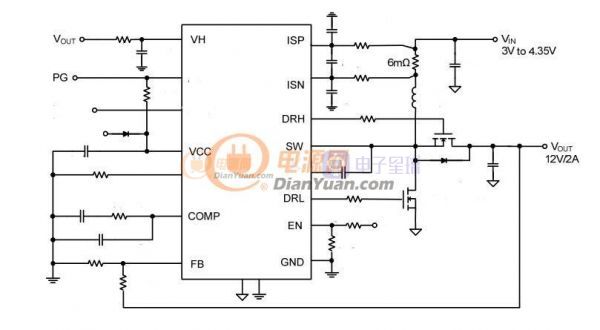

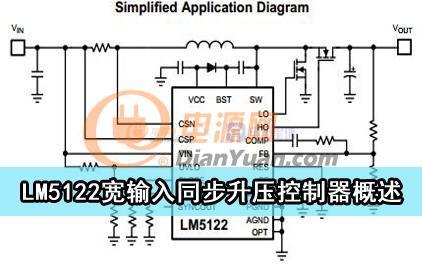

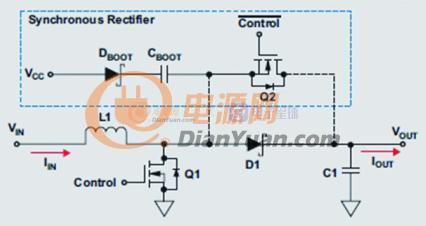

BUCK、BOOST这些非隔离的内部MOS管驱动信号给完后经过死区就给同步整流MOS驱动信号,检测电流过零后关断。再就是可根据反馈确定是否进入同步整流模式,毕竟对于轻空载,开关损耗成分会升高。