本篇文章将介绍三极管设计逻辑取反电路,希望与大家一起学习进步!也欢迎读者朋友关注、收藏、分享和点赞,感谢支持!

数字电路里面经常会用到一些逻辑门,比如“与门”、“或门”,“非门”等门电路;模拟电路里面经常会将TTL电平转换为CMOS电平。无论是门电路还是电平转换电路的设计,几乎都离不开三极管。下面将分析模拟电路中的“逻辑取反”电路也是数字电路里面的“非门”,从无到有的设计过程,一起看看简单的电路里面包含的内容。

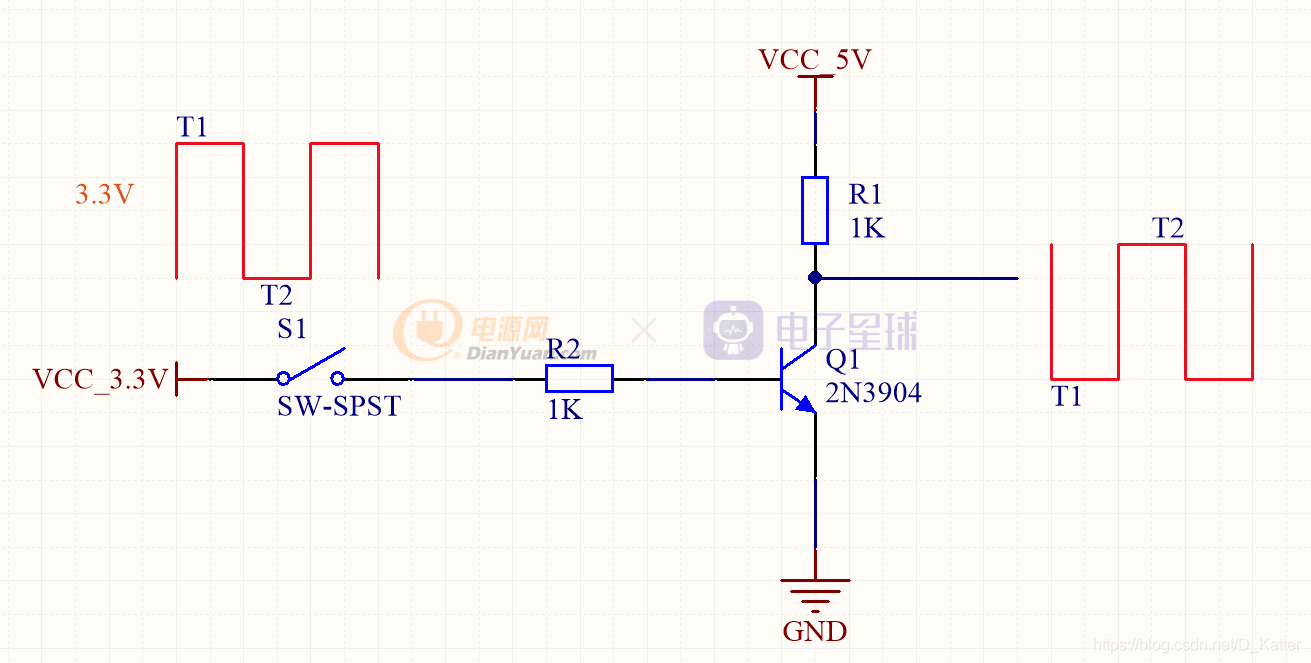

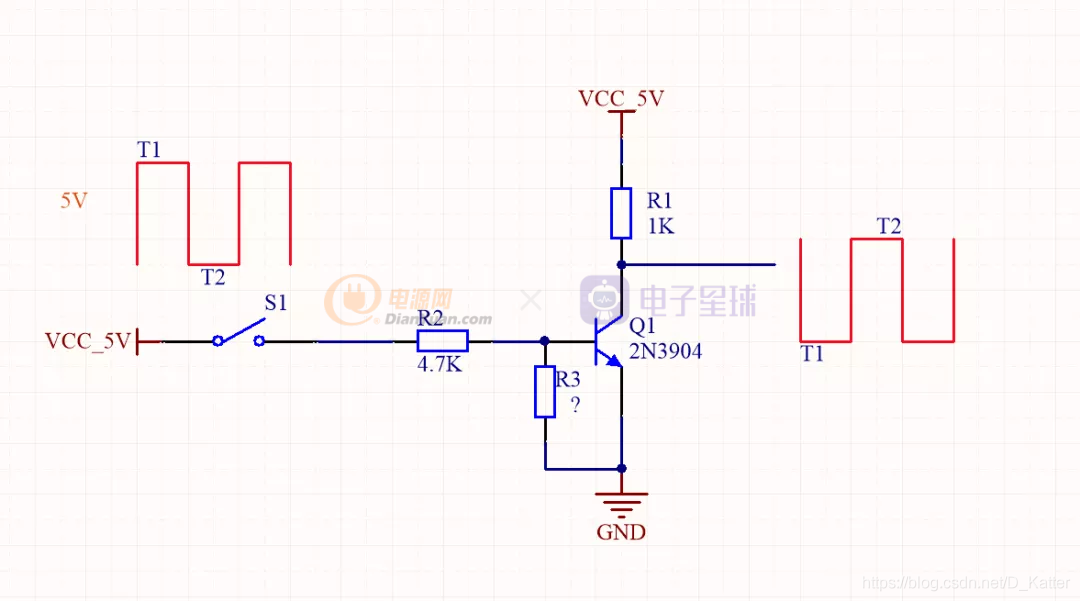

上面这个电路应该都很熟悉,它经常用在电平转换电路中。由上图所示,控制信号为3.3V,但是在三极管的集电极,即Vce可以达到5V,能够实现电平的转换。

另外,从控制电路的脉冲信号和输出电压Vce的波形相位可以看出:当控制信号为高电平时,输出信号为0V;当控制信号为低电平时,输出信号为5V。如果我们将控制信号的电平和R1上端的VCC_5V两者进行统一,则电路实现了逻辑取反的功能。

经过上面的分析,电路在理论层面,实现功能上没什么问题,那是不是这个电路的设计就是合理的呢?可以准确的说,不是。

01.不合理之一:三极管基级电阻取值

三极管属于流控流型的三端器件,当Vbe≥0.7V时,即Ib流过一个电流,Ic就有电流流过。而无论是逻辑取反电路,还是电平转换电路,三极管都是用作“开关”,即使用三极管的“饱和”和“截止”两个状态。

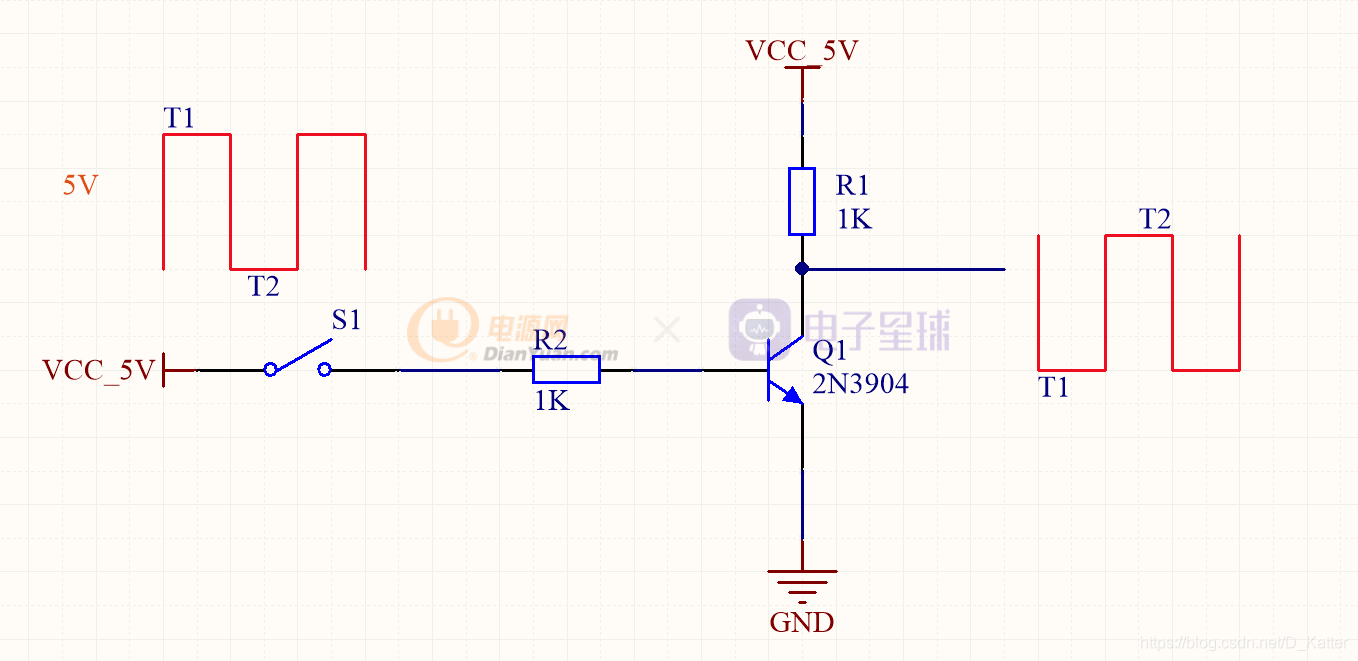

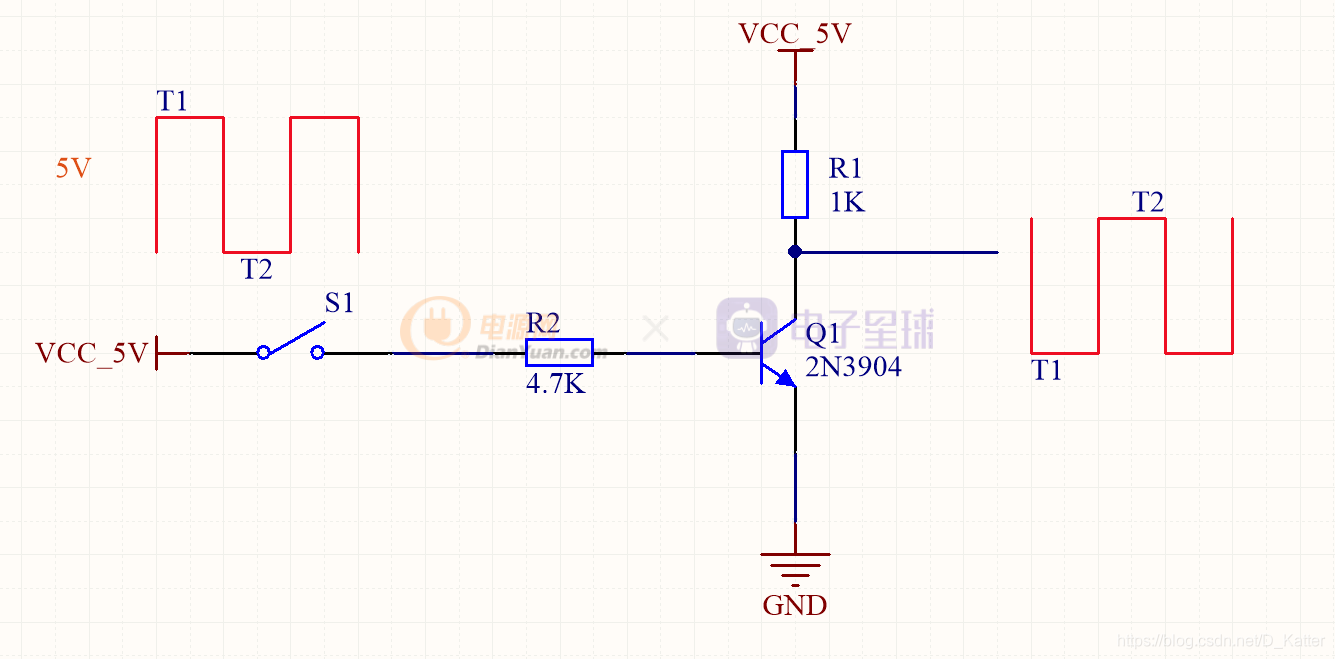

为了上述电路能正常工作,必须使Ib≥1mA,三极管才能完全导通,工作在饱和导通状态。由于控制信号为5V,则R2取值为5k能满足条件。考虑到电阻取值,这里取4.7k。R1为上拉电阻,这里取1k。为什么R2取1k不好呢?这里是从功耗的层面出发。由控制信号为5V,Vbe=0.7V,则电阻R2的功率由P=U²/R,当R2增大,功耗是减小的。

02.不合理之二:三极管基极出现高组态

在一个电路里面,任何一个半导体器件只允许有两个状态,要么是接高电平,要么是接低电平(有的芯片手册上也看到,不用的引脚浮空,这里不做讨论),就是为了避免出现高阻态的情况出现。高阻态意味着三极管的基极是一个不稳定的状态。

当S1开关导通时,三极管的基极此时为高电平;当S1开关断开时,三极管的基极此时接R2,但是R2的左端悬空,即三极管的基极为高阻态(电平不确定)。既然电平不确定,就存在下面三个问题:

- 静电

- 雷击

- 电磁干扰

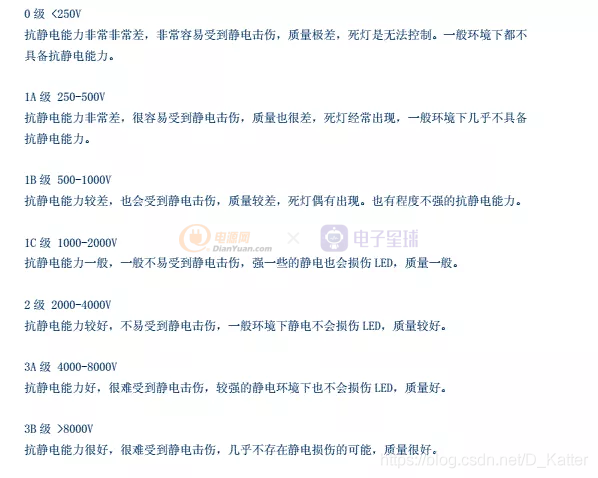

静电大家比较熟悉,冬天穿好衣服如果立马去开自己的笔记本电脑,经常会出现触电的感觉,这就是静电。而接触放电在瞬时可以达到4kV,如果刚好这个静电接触到R2的左端,那么三极管在这一瞬间就会误导通,甚至是损坏。所以经常会在产品上看到ESD防护等级要求,就是为了保证产品能过静电干扰。

雷击和静电破坏原理差不多,如果产品用在室外,碰上雷雨电气,R2左端会存在被几十KV雷击的危险,也会造成三极管的误导通,而且肯定被烧毁。

电磁干扰是因为在空气中存在着大量的电磁波,如果刚好在某个时候,周围存在一个非常大的电磁波被电路吸收,那么三极管还是存在误导通的风险。

因此,为了避免上面三种情况的发生,就要避免三极管的基极出现高阻态的情况。于是就在三极管的基极增加下拉电阻R3,保证开关断开时,基极接地。但是问题来了,R3的取值为多大呢?

R3的取值,从两个方面考虑,

-

流过三极管基极的电流Ib≥1mA

-

Vbe≥0.7V

由于R2的取值能够保证Ib,那是不是R3取2K,4.7K,5.6K 等,只要满足Vbe≥0.7V就可以呢?

03.不合理之三:没考虑三极管实际特性

半导体器件和导体不一样,像电阻是导体,流过电阻两端的电压和电流是同相位,但是半导体器件由于生产工艺的原因,无法避免的在一些器件上产生了寄生电容也叫杂散电容。三极管的开通和关断就不能按照电阻那样分析,开关闭合,三极管立马开通;开关关断,三极管立马关断,这是理想的状态。对于实际的电路,三极管的开通也是需要时间的。三极管的等效电路如图所示(不考虑Cbc和Cce对电路的影响)。

三极管要开通,基极将经历下面的过程:

-

Ib电流对电容Cbe充电

-

Cbe达到0.7V以后,三极管导通

-

Cbe对be等效的PN结放电-

三极管完全导通时,此时Vce为0,三极管工作在饱和区;三极管完全关闭时,此时Vce为5V,三极管工作在截止区。Vce从0到5V的过程即为三极管关断的过程,此过程中间有一个放大状态,而放大状态是我们设计并不希望它出现的,因此三极管的关断要越快越好。显然Cbe对整个电路的无论是在开通还是在关断,都起到阻碍的作用。

为了加快三极管的开通,可以略微减小R2,能增加充电的电流;为了加快三极管的关断,R3的取值显然并不是越大越好。

根据经验值,三极管的基极电阻R2取3.3K,R3取2K,是比较合适的。

从上面的分析可以看出,一个简单的电路要设计好,包含的内容真的是太多了,功能上的实现只是理论层面的分析,真正用在产品上的电路,是需要经过多方面的考虑,包括封装,型号,价格,功耗,可制造性等等问题。

最后设计的逻辑取反电路如下图所示。

欢迎读者朋友关注、收藏、分享和点赞,感谢支持!