时钟管理

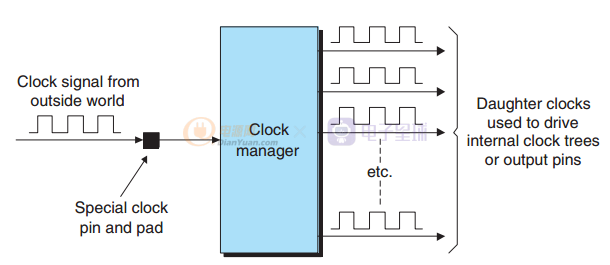

与其他芯片配置时钟引脚直接连接到内部的时钟树不同,FPGA可以用来驱动一个称为时钟管理器的特殊硬连线功能(块),再生成多个子时钟。

这些子时钟可以驱动内部时钟树,也可以通过外置引脚进行时钟的输出。每个系列的FPGA都会有自己的时钟管理(一个FPGA可能也会有多个时钟管理块)。FPGA的时钟管理块的功能非常强大,一般都拥有以下特点:

1、时钟抖动消除(移除时基误差)。一个简单的例子,假设一个1MHz的时钟(实际应用中可能更高)。理想情况中,一个1MHz的时钟,后一个时钟沿比前一个时钟沿要晚到1us进入芯片。但是在实际中,情况确实可能会发生提前或延后。如果有示波器能够观察这个现象的话,你会发现,这个时钟的上下沿之间的宽度是会变化的,是一个边沿呈现模糊的时钟。FPGA的时种管理块能够检测并修正这样的时种抖动,从而给后续的功能块提供“干净稳定”的子时钟。如下图所示:

2、频率合成。有时候,外部提供的时钟可能并不是设计人员需要的,需要降频或者倍频。在这种情况下,时钟管理器可以用来产生子时钟,子时钟的频率是由原始时钟频率的乘或除得到的。在实际应用中,基本上可以直接从原时钟获得工程上所期望的时钟频率。如下图所示:

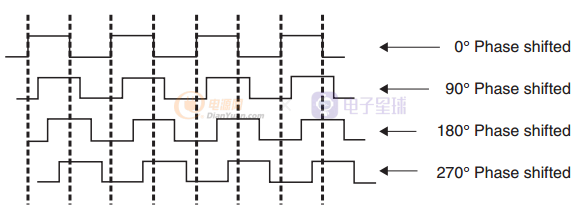

3、时钟相移。在实际的工程中,有些设计还需求确定时钟的相移,一些时钟管理器允许您从普通值的固定相移中进行选择,例如120°和240°(对于三相时钟方案)或90°、180°和270°(如果需要四相时钟方案)。还有一些允许您配置每个子时钟所需的相移的确切数量。如下图所示:

4、自动偏差修正。有时候,后续的功能块需要的子时钟与原输入的时钟要求相同,同频率同相位。但是时钟信号在经过时钟管理块处理后,会有略微延迟的现象,这将会提高后续功能块处理的不确定性。结果就是,不做任何修正的话,子时钟将会比原时钟慢一些。这就是所谓的两个时钟之间固有的偏差。如果不做处理,这可能导致,FPGA中使用主时钟的功能块和使用子时钟的功能块会导致一些问题。一般做法是,通过使子时钟经过额外的延迟模块,达成与主时钟的匹配。

PS:一些FPGA时钟管理器基于锁相环(PLLs),而另一些基于数字延迟锁定环(DLLs)。自20世纪40年代以来,锁相环就被用于模拟实现,但最近对数字方法的强调使得数字匹配信号相位成为可取的。锁相环(PLLs)可以使用模拟或数字技术来实现,然而,DLLs就是基于数字技术的。

PS:DLLs在精度、稳定性、电源管理、噪声不敏感和抖动性能方面更具有优势。

这篇介绍了FPGA的时钟管理块。下一篇介绍大家最关心的FPGA的GPIO篇。