‹ 保持不同的踪迹紧密相连。 将噪声注入保持为在差分系统中衰减的共模信号。

‹ 保持不同的踪迹紧密相连。 将噪声注入保持为在差分系统中衰减的共模信号。

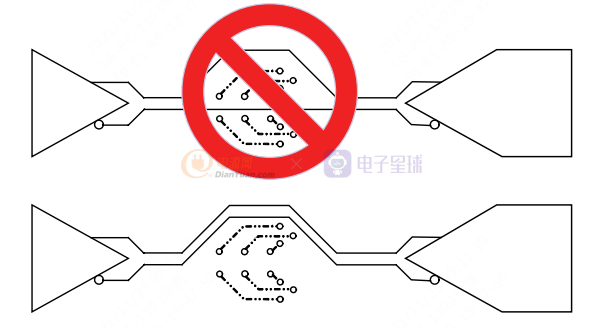

‹ 将差分走线绕障碍物一起布线,不要分开。

‹ 尽量保持走线长度完全相同,以保持延迟相等。

在布线差分走线时,它们应始终布线在一起(并排)。 这使任何注入信号的噪声都成为真正的共模噪声,被接收器拒绝。 如果噪声只进入一个通道而不进入另一个通道,则抑制量充其量是最小的。

此外,两条走线的长度应保持相同。否则信号可能会在不同时间到达接收器并导致性能问题。 对于非常快速的开关数字信号和非常高的模拟信号 (>1-GHz) 尤其如此。

微带

微带

‹最常用

‹更少的传播延迟

‹可能辐射更多射频

‹只需要2层

带状线

带状线

‹更多传播延迟

‹更好的抗噪/辐射

‹至少需要3层

‹可能更难控制Z0

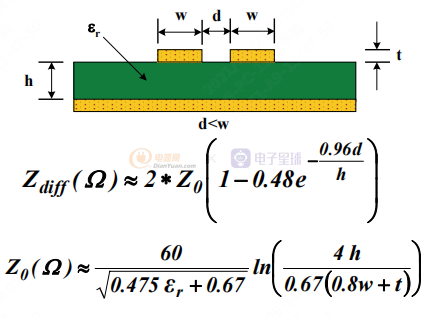

就像单条走线一样,差分走线也可以具有由电感和电容决定的特性阻抗。 保持差分走线靠近是非常可取的,因为它可以最大限度地减少噪声注入问题并最大限度地减少辐射电磁场。

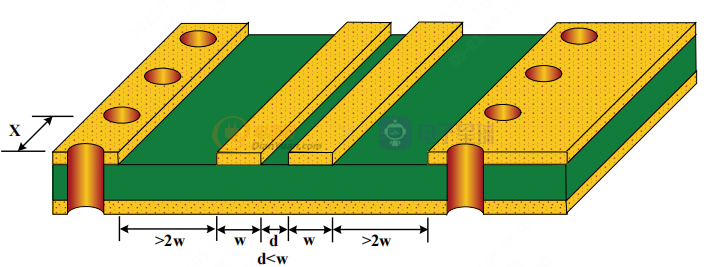

‹ 常见于顶层和平面层上的 GND 平面。

‹ 常见于顶层和平面层上的 GND 平面。

‹同层的GND平面应≥2倍走线宽度。 减少辐射磁场面积以及对外部信号的敏感性。

‹ 确保使用多个过孔并放置在信号走线附近。

‹ 过孔间距 (X) 应≤ 0.25cm (≤0.1”)。

通常在信号层上使用接地层。 这样做的一个好处是它减少了走线上信号的辐射磁场。 如果使用相邻的地平面,最好使走线和地平面之间的距离至少等于走线宽度距离的两倍。 这最大限度地减少了平面的电容,该电容可以改变走线的特征阻抗。 因为走线和同层接地区域之间会有一些电容,所以会有一些电流流过这个电容。 为了尽可能减少电流回路面积,最好放置将两个平面连接在一起的过孔。 在整个走线长度上,这些过孔彼此之间的间距不应超过 0.25 厘米(0.1 英寸)。