本篇文章来自:机智的互联网

1、前言

低压降稳压器 (LDO) 的典型特性必然是压降。毕竟,其名称及其缩写由此而来。从根本上讲,压降描述的是正常稳压所需的 VIN 和 VOUT 之间的最小差值。

2、什么是压降?

压降电压 VDO 是指为实现正常稳压,输入电压 VIN 必须高出所需输出电压 VOUT(nom) 的最小压差。请参见 公式 1:

公式 1:VIN ≥ VOUT(nom) + VDO

如果 VIN 低于此值,线性稳压器将以压降状态工作,不再调节所需的输出电压。在这种情况下,输出电压 VOUT(dropout) 将等于 VIN 减去压降电压的值(公式 2):

公式 2:VOUT(dropout) = VIN − VDO

以调节后电压为 3.3V 的 TPS799 等 LDO 为例:当输出 200mA 电流时,TPS799 的最大压降电压指定为 175mV。只要输入电压为 3.475V 或更高,就不会影响调节过程。但是,输入电压降至 3.375V 将导致 LDO 以压降状态工作并停止调节,如图 1 所示。虽然应将输出电压调节为 3.3V,但 TPS799 没有保持稳压所需的余量电压。因此,输出电压将开始跟随输入电压变化。

图 1 在低压降状态下工作的TPS799

3、决定压降的因素是什么?

压降主要由 LDO 架构决定。 为说明原因,让我们来了解一下 P 沟道金属氧化物半导体 (PMOS) 和 N 沟道 MOS (NMOS) LDO,并对比其工作情况。

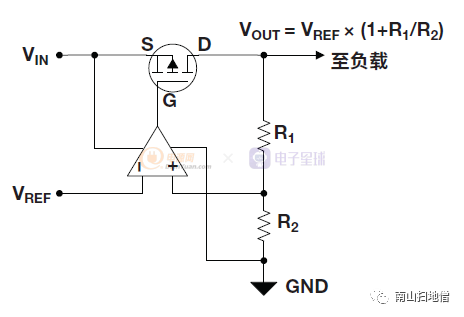

3.1、PMOS 架构 LDO

图 2 所示为 PMOS LDO 架构。为调节所需的输出电压,反馈回路将控制漏-源极电阻 RDS。随着 VIN 逐渐接近 VOUT(nom),误差放大器将驱动栅-源极电压 VGS 负向增大,以减小 RDS,从而保持稳压。

图 2 PMOS LDO

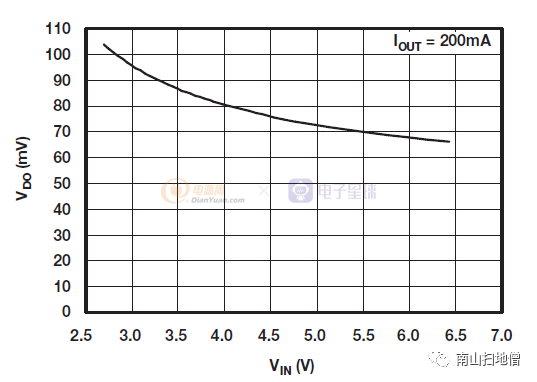

但是,在特定的点,误差放大器输出将在接地端达到饱和状态,无法驱动 VGS 进一步负向增大。RDS 已达到其最小值。将此 RDS 值与输出电流 IOUT 相乘,将得到压降电压。请记住,随着 VGS 负向增大,能达到的 RDS 值越低。通过提升输入电压,可以使 VGS 值负向增大。因此,PMOS 架构在较高的输出电压下具有较低的压降。图 3 展示了此特性。

图 3 TPS799 的压降电压与输入电压关系图

如图 3 所示,TPS799 的压降电压随输入电压(也适用于输出电压)增大而降低。这是因为随着输入电压升高 VGS 会负向增大。

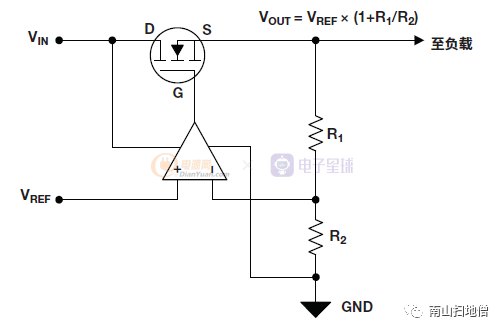

3.2、NMOS 架构 LDO

NMOS 架构如图 4 所示,反馈回路仍然控制 RDS。但是,随着 VIN 接近 VOUT(nom),误差放大器将增大 VGS 以降低 RDS,从而保持稳压。

图 4 NMOS

LDO在特定的点,VGS 无法再升高,因为误差放大器输出在电源电压 VIN 下将达到饱和状态。达到此状态时,RDS 处于最小值。将此值与输出电流 IOUT 相乘,会获得压降电压。不过这也会产生问题,因为误差放大器输出在 VIN 处达到饱和状态,随着 VIN 接近 VOUT(nom),VGS 也会降低。这有助于防止出现超低压降。

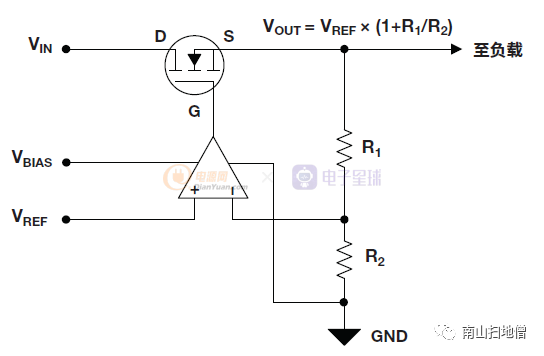

3.3、偏置 LDO

很多 NMOS LDO 都采用辅助电压轨,即偏置电压 VBIAS,如图 5 所示。

图 5 带偏置电压轨的 NMOS LDO

此电压轨用作误差放大器的正电源轨,并支持其输出一直摆动到高于 VIN 的 VBIAS。这种配置能够使 LDO 保持较高 VGS,从而在低输出电压下达到超低压降。有时并未提供辅助电压轨,但仍然需要在较低的输出电压下达到低压降。在这种情况下,可以用内部电荷泵代替 VBIAS,如图 6 所示。

图 6 带内部电荷泵的 NMOS LDO

电荷泵将提升 VIN,以便误差放大器在缺少外部 VBIAS 电压轨的情况下仍可以生成更大的 VGS 值。

3.4、其他因素

除了架构之外,压降还会受到其他一些因素的影响,如表 1 所示。

表 1 影响压降的因素

很显然,压降并不是一个静态值。虽然这些因素会提高选择 LDO 的复杂程度,但同时,还能帮助您根据特定的条件选择最适合的 LDO。以上关于LDO基础特性压降部分就为大家讲解完成了,喜欢的可以点个早看或者转发哦~

------------ END ------------