任何的EMC及电子电路的可靠性设计疑难杂症;先分析再设计才是高性价比的设计!

更多设计应用实践及技术交流;请关注阿杜老师!

在EMC设计过程中,电容器是应用最广泛的器件,主要用于构成各种低通滤波器或用作去耦电容和旁路电容。通过实践数据:在EMC设计中,恰当选择与使用电容,不仅可以解决许多EMC问题,还能充分体现比较好的效果及使用时比较方便的优点。如果电容的选择或者使用不当,则可能达不到预期的目的,甚至会恶化产品的EMC水平。

-

电容的自谐振

电容器是基本的滤波器件,在低通滤波器中作为旁路器件使用。利用它的阻抗随频率升高而降低的特性,可起到对高频干扰旁路的作用。但是,在实际使用中一定要注意电容器的非理想性。

从理论上看,理想的电容容量越大,容抗就越小,滤波效果就越好。但是,电容器都存在等效串联电感ESL,容量大的电容器一般等效串联电感也大,而且等效串联电感与电容本身呈串联关系,于是串联自谐振就产生了,等效串联电感越大,自谐振频率越低,对高频噪声的去耦效果也越差,甚至根本起不到去耦作用。元件的物理尺寸越大,同样容值的电容器其自谐振点频率越低。

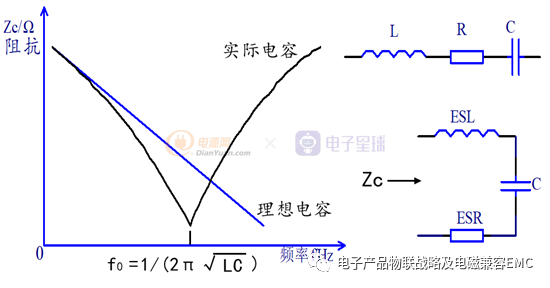

实际电容器的电路模型及频率阻抗特性如下图所示,它是由等效电感ESL、电容和等效电阻ESR构成的串联网络。电感分量是由引线和电容结构所决定的,电阻是介质材料所固有的。电感分量是影响电容频率特性的主要指标,因此在分析实际电容器的旁路作用时,用LC串联网络来等效。

电容器的等效电路及频率阻抗特性

如图所示,在谐振频率f0上,L和C将串联谐振,此时整个回路的阻抗最低。在自谐振点以上的频率,电容的阻抗随感性的增加而增加,这时电容将不再起旁路和去耦的作用。因此,旁路和去耦受电容器的引线电感及电容和元器件间布线长度、通孔焊盘等的影响。

2.电容对滤波特性的影响

实际的电容器如上图所示,当f0=1/(2π(LC)1/2)时,会发生串联谐振,这时电容的阻抗最小,旁路效果最好。超过谐振点后,电容器的阻抗特性呈现电感的阻抗特性。随着频率的升高而增加,旁路效果开始变差。这时,作为旁路器件使用的电容器开始失去旁路的作用。

理想电容的阻抗是随着频率的升高而降低,而实际电容的阻抗,在频率较低时,呈现电容特性,即阻抗随频率的增加而降低,在某一点发生谐振,在这点电容的阻抗等于等效串联电阻ESR。在谐振点以上,由于ESL的作用,电容阻抗随着频率的升高而增加,因此对高频噪声的旁路作用减弱,甚至消失。

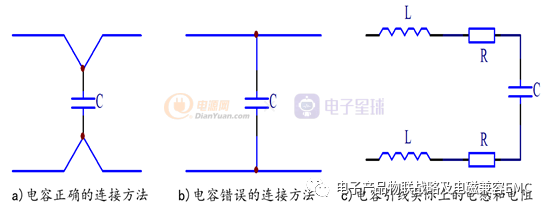

电容的谐振频率由ESL和C共同决定,电容值或电感值越大,谐振频率越低,也就是电容的高频滤波效果越差。ESL除了与电容器的种类有关外,电容的引线长度也是一个非常重要的参数,引线越长,则电感越大,电容的谐振频率越低。因此在实际的应用中,要使电容器件的引线尽量短,电容器的正确设计方法和不正确的连接方式如下图所示。

滤波电容器正确与错误连接方式示意图

根据LC电路串联谐振的原理,谐振点不仅与电感有关,还与电容值有关,电容越大,谐振点越低。有许多的设计工程师认为电容器的容值越大,滤波效果越好,这是一种误解。电容越大,对低频干扰的旁路效果虽然好,但是由于电容在较低的频率发生了谐振,阻抗开始随着频率的升高而增加,因此对高频噪声的旁路效果变差。

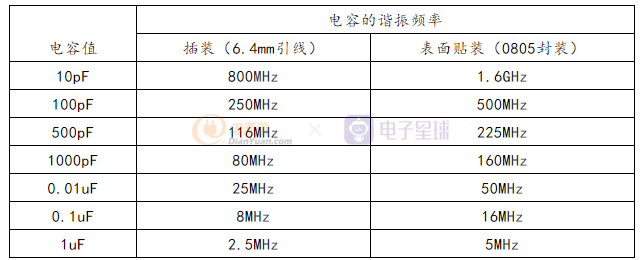

因此,在选择电容器时,并非取决于电容值的大小,而是电容器的自谐振频率,并与逻辑电路和所用的工作频率相匹配。在自谐振频率以下电容器表现为容性,在自谐振频率以上电容器变为感性。当电容器表现为感性时,实际上已经失去了电容应有的作用。在下表中显示了两种类型的瓷片电容的自谐振频率。一种是带有6.4mm引脚的,另一种是表贴0805封装的。

电容器的自谐振频率

注意:表中对于插件的寄生电感估算值L=3.75nH;0805封装寄生电感估算L=1nH。

尽管从滤除高频噪声的角度看,不希望有电容谐振,但是电容的谐振并不总是有害的。当要滤除的噪声频率确定时,可以通过调整电容的容量,使谐振点刚好落在骚扰频率上。

电磁兼容设计中使用的电容要求频率尽量高,这样才能够在较宽的频率范围(10KHz~1GHz)内起到有效的滤波作用。提高谐振频率的方法有两种:一种是尽量缩短引线的长度;另一种是选用电感较小种类的电容器件。

在表中,以1uF电容为例,插装(6.4mm引线)的高频电容的谐振点为2.5MHz在谐振点其阻抗最小。其表面贴装(0805封装)的高频电容的谐振点为5MHz在谐振点其阻抗最小。

通过上表的参考数据,该类器件的引线过长时,其高频下寄生参数会降低自身的谐振频率,在进行高频滤波时建议尽量采用贴装器件。一个常用的做法是选择参数相差100倍的电容进行并联,以保证在其较宽的频段范围内始终保持电容特性。

但在实际应用时,由于电容放置时电容引脚及走线离数字芯片的距离差异会带来不同的引线或走线电感,同时大的容量能起到储能滤波的作用。因此,对于数字芯片做去耦设计,特别是携带丰富高次谐波的数字电源引脚,通常用大容量电容与0.1μF电容及0.1uF的多个同容值电容并联,有更好的效果。

表贴电容器的自谐振频率相对较高,在实际应用中,它的连接线的等效串联电感也会减小其原来的优势。表贴电容器有较高的自谐振频率是因为小包装尺寸的径向和轴向的电容的引线电感较小。根据实际经验,不同封装尺寸的表贴电容,随着封装的引线电感的变化,它的自谐振频率的变化在±(2~5)MHz之内。

插件的电容器只不过是表贴器件加上插脚引线的结果。对于典型的插件电容,它的等效串联电感平均为2.5nH/2.54mm。表贴电容器的等效串联电感平均为1nH。综合以上所述,在使用去耦电容时电容的等效串联电感时需要重点考虑的。表贴电容器比插件电容器高频时有更好的效能,就是因为它的等效串联电感很低。

既然等效的串联电感是引起电容在自谐振频率以上失去其应用的主要因素,那么在实际电路应用中,必须将PCB中电容的连接线电感包括过孔等影响因素都考虑进去。在某些电路,如果工作频率很高,而且频率要比电容在电路中呈现的自谐振频率范围高很多,那么就不能使用该电容。

比如,一个0.1uF的电容不适合给100MHz时钟信号去滤波,而0.001uF电容在不考虑引线及过孔的电感情况下,就是一个很好的选择。这是因为100MHz及其谐波已经超过了0.1uF电容的谐振频率。

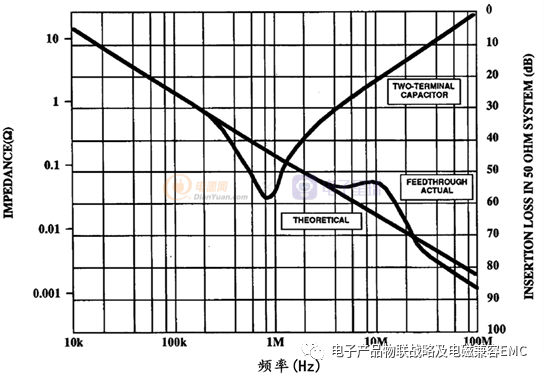

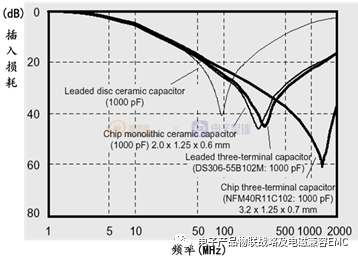

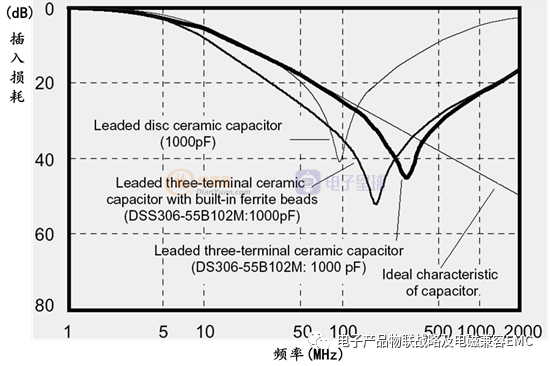

在实际应用中,一般选择瓷片电容,超小型聚酯或聚苯乙烯薄膜电容也是可以的,它们的尺寸与瓷片电容相当。还有一种三端电容因为电容引线电感极小,它可以将小瓷片电容的频率范围从50MHz以下扩展到200MHz以上,这对抑制较高频段的噪声是很有用的。要在较高频段或更高的频段获得更好的滤波效果,特别是保护屏蔽体不被穿透,必须使用馈通电容,这是三端电容的一种。

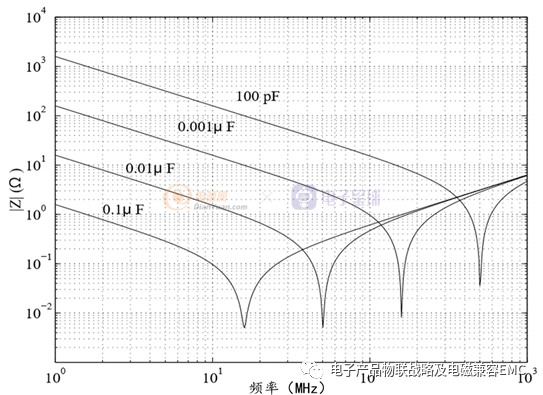

下图分别是不同电容及容值的电容器的频率阻抗关系图,从图中可以看出自谐振频率点,可供参考。

常用陶瓷电容不同容值电容的频率阻抗关系图

常用插件不同容值的电容器件的频率与阻抗关系图

注:图示中的寄生电感ESL为35nH,电容ESR为50mΩ。

常用表贴不同容值的电容器件的频率与阻抗关系图

注:图示中的寄生电感为1nH,电容ESR为5mΩ。

穿心电容器件的频率阻抗及插入损耗特性

不同贴片三端电容器件的插入损耗特性

三端电容与普通电容器件的插入损耗对比特性

PCB中电源层与地平面之间的分布电容是理想的平板电容,电流一律从一边流入,从另一边流出,电感几乎为0。在这种情况下,平板电容在高频时仍然表现为容性,因此在多层板PCB设计时,电源层与地层之间形成的平板电容对高频数字电路的高频去耦具有重要意义,PCB中电源层与地层之间形成的平板电容大小随着电源层与地层之间距离的减小而增加,随着电源层与地层面积的增大而增大。因此,在数字电路中增加的高频电容与平板电容之间存在并联关系,相当于电容器的并联。这样在电路中就会出现并联电容的反共谐振点。

作者简介:杜佐兵

电磁兼容(EMC)线上&线下高级讲师

杜佐兵老师在电子行业从业近20年,是国家电工委员会高级注册EMC工程师,武汉大学光电工程学院、光电子半导体激光技术专家。目前专注于电子产品的电磁兼容设计、开关电源及LED背光驱动设计。