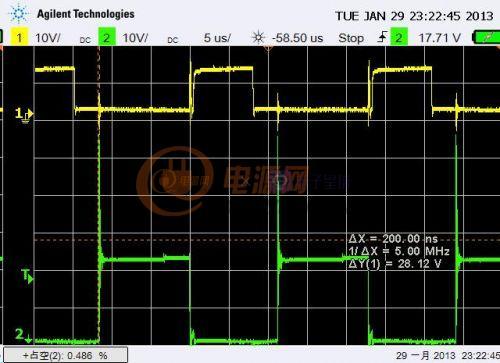

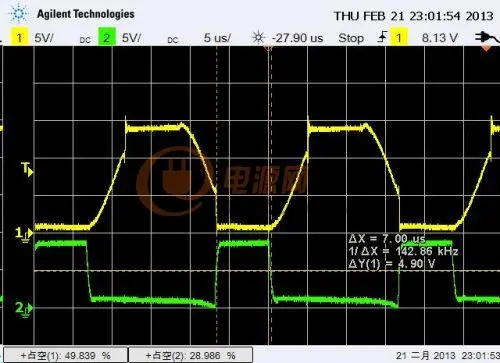

两片IR2110出来的PWM信号直接驱动全桥,母线电压24V,可是在PWM占空比改变的情况下,MOS管VDS的占空比始终保持最大占空比不变,如下图所示。黄色为驱动波形,绿色为VDS波形。由于是自己搭接的电路,波形不是很好。请大神们帮我分析下。不胜感激...

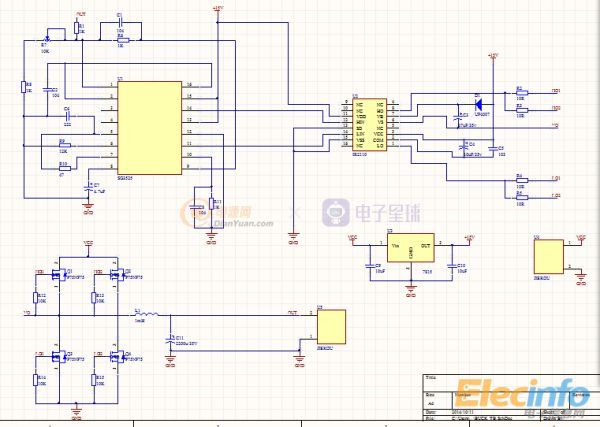

SG3525+IR2110+全桥,遇到怪问题,希望大神们不吝赐教...

全部回复(19)

正序查看

倒序查看

现在还没有回复呢,说说你的想法

@米山人家

才24V波形就这么差了如果是超过100V,你来不及抓图,板子就炸掉了 1,死区时间太大,2,驱动过强3,另外还有一种可能就是,全桥工作在容性状态,你的驱动频率,低于LC的谐振频率,电流相位超前了但要首先把第一点排除掉再说

谢谢您的指教

1. 这个死区是我故意调出来的,想看看改变死区时间会不会让VDS有所改变。之前死去时间非常小的时候,情况一样。

2. IR2110驱动40A/600V的MOS管驱动能力应该不是过强吧。

3. 现在频率是50K左右,我将频率升到100K时,问题同样存在。这点我再验证一下。请问还有其他可能的原因吗?

再次感谢!

0

回复

提示

@chandlar

谢谢您的指教1.这个死区是我故意调出来的,想看看改变死区时间会不会让VDS有所改变。之前死去时间非常小的时候,情况一样。2.IR2110驱动40A/600V的MOS管驱动能力应该不是过强吧。3. 现在频率是50K左右,我将频率升到100K时,问题同样存在。这点我再验证一下。请问还有其他可能的原因吗?再次感谢!

死区时间一定不能过大,如果你要观察VDS的变化情况,可以用其它方式

2110的驱动方面,你自己分析,我不解释

如果频率升到100K仍存在同样问题,那么你的主电路肯定有哪里没处理好

你的LC是串联还是并联,如果是并联的话,就当我没说过

0

回复

提示

@chandlar

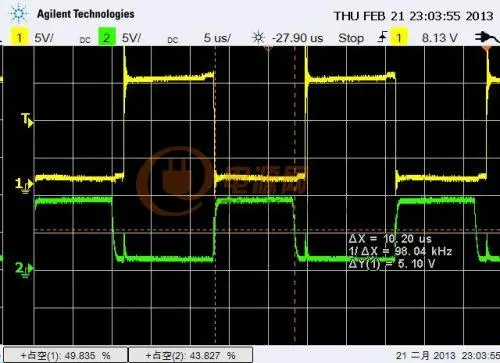

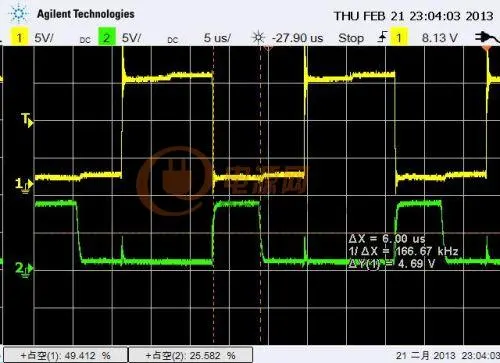

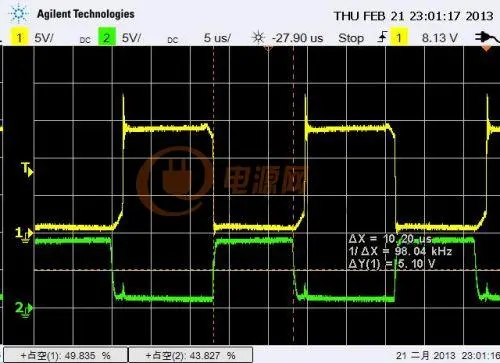

IR2103+SG3525,全桥电路。年后又调试了下,发现问题仍然没有解决,奇了怪了,上几张波形图。1.未带高频变压器,最大占空比。[图片] 2.未带高频变压器,调小占空比。[图片] 3.带2.5K电阻负载,最大占空比。[图片] 4.带2.5K电阻负载,将占空比减小。[图片] MOS管是40A/500V的IRFPS40N50L,驱动IC改用IR2103后加图腾输出驱动MOS。调试时母线电压采用15V。逆变频率是100K。主电路MOS带RC缓冲电路,为减小Cds的影响,在MOS的GS间并了100PF的电容。请大侠帮忙分析一下,晚辈感激不尽。

电阻减小,或者简单点你用2~3个200W的白炽灯串联作为负载,你就会看到你想要的波形了

0

回复

提示